### NASA-CR-191799

12/26/92

And the second second second

### PROPRIETARY NOTICE

### SBIR RIGHTS NOTICE (APRIL 1985)

This SBIR data is furnished with SBIR rights under NASA Contract No. <u>NAS5-30633</u>. For a period of 2 years after acceptance of all items to be delivered under this contract the Government agrees to use this data for Government purposes only, and it shall not be disclosed outside the Government (including disclosure for procurement purposes) during such period without permission of the Contractor, except that, subject to the foregoing use and disclosure prohibitions, such data may be disclosed for use by support contractors. After the aforesaid 2-year period the Government has a royalty-free license to use, and to authorize others to use on its behalf, this data for Government purposes, but is relieved of all disclosure prohibitions and assumes no liability for unauthorized use of this data by third parties. This Notice shall be affixed to any reproductions of this data, in whole or in part.

The specific data to which this notice applies is contained on pages 2-12 through 2-18, 2-24 through 2-30, 2-32 through 2-40 and 4-1 through 4-10.

### TABLE OF CONTENTS

| 1 | I. Introduction                                                                                | 1-1              |

|---|------------------------------------------------------------------------------------------------|------------------|

|   | 2. DDSC and DSCN Descriptions                                                                  | 2-1              |

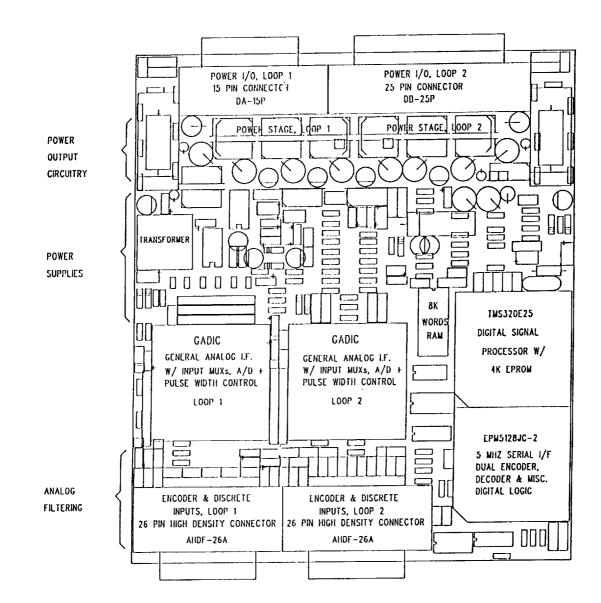

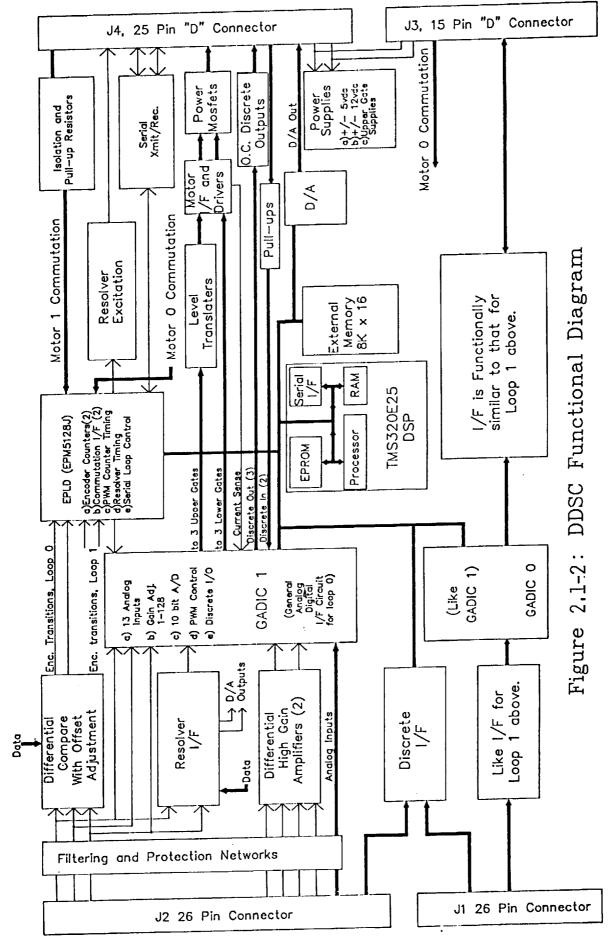

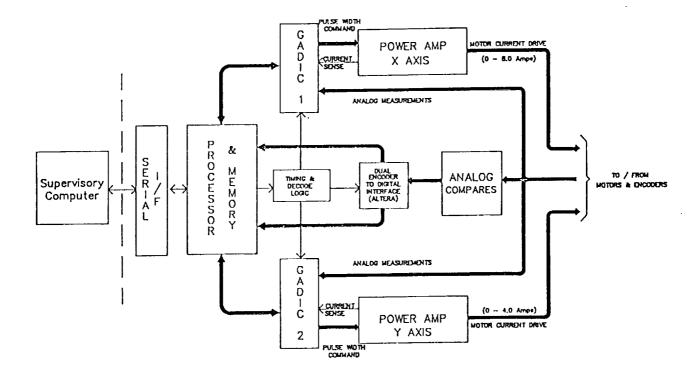

|   | 2.1 DDSC Description                                                                           | 2-1              |

|   | 2.1.1 Overall DDSC                                                                             | 2-1              |

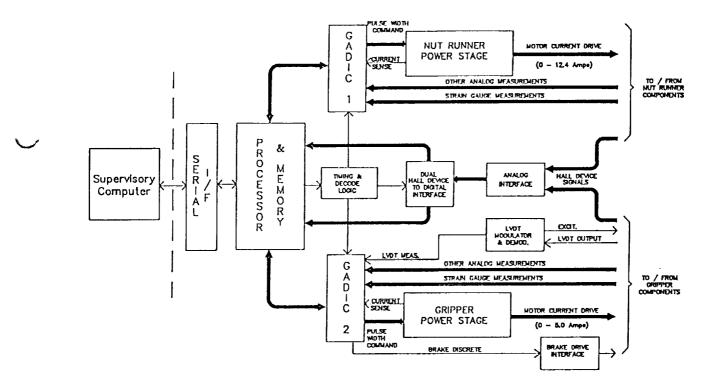

|   | 2.1.2 Major DDSC Components                                                                    | 2-5              |

|   | 2.1.2.1 TMS320E25 DSP                                                                          | 2-5              |

|   | 2.1.2.2 General Analog/Digital Interface Circu                                                 | it               |

|   | (GADIC)                                                                                        | 2-5              |

|   | 2.1.2.3 Electrically Programmable Logic Devi                                                   | се               |

|   | (EPLD)                                                                                         | 2-5              |

|   | 2.2 Navtrol's DSCN System                                                                      | 2-8              |

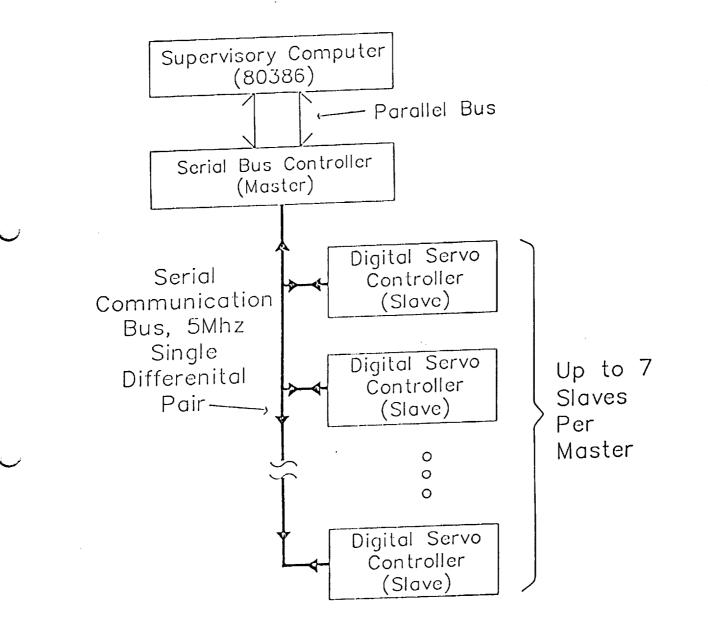

|   | 2.2.1 A Network of Controllers                                                                 | 2-8              |

|   | 2.2.2 The Master Controller and Supervisory Computer                                           | 2-8              |

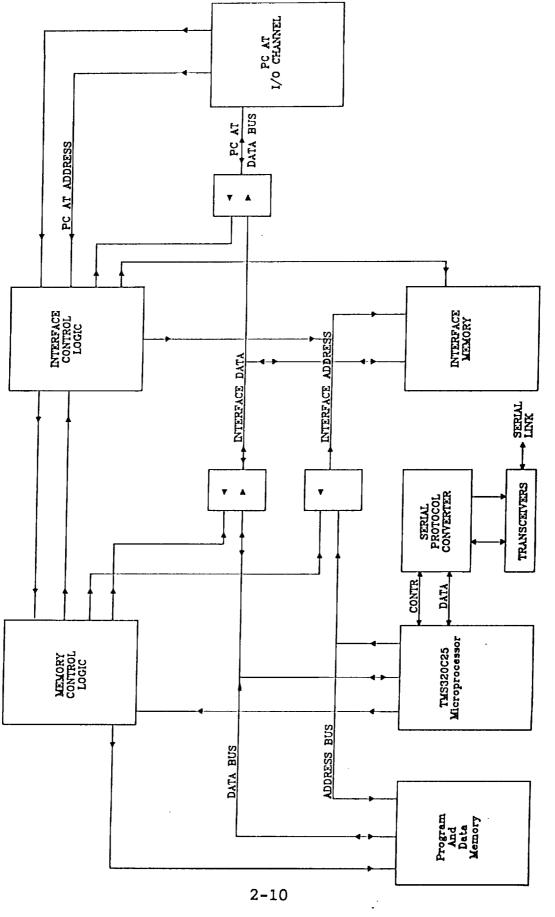

|   | 2.2.3 DEMON Servo Development System                                                           |                  |

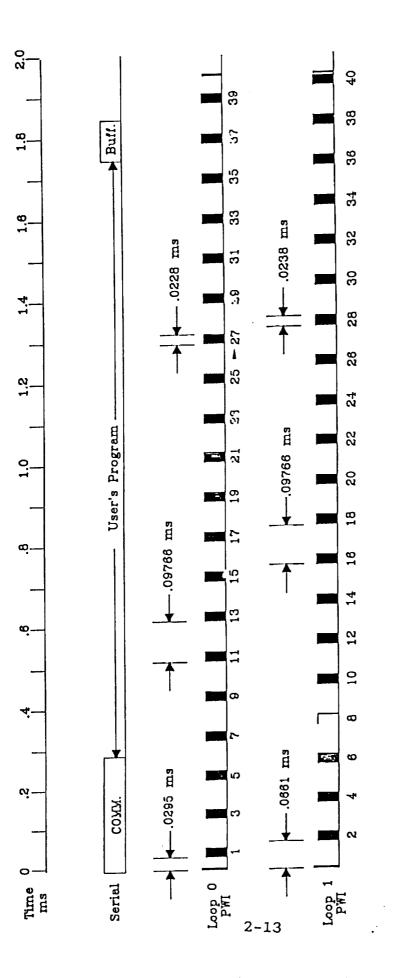

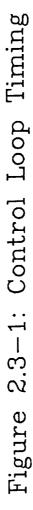

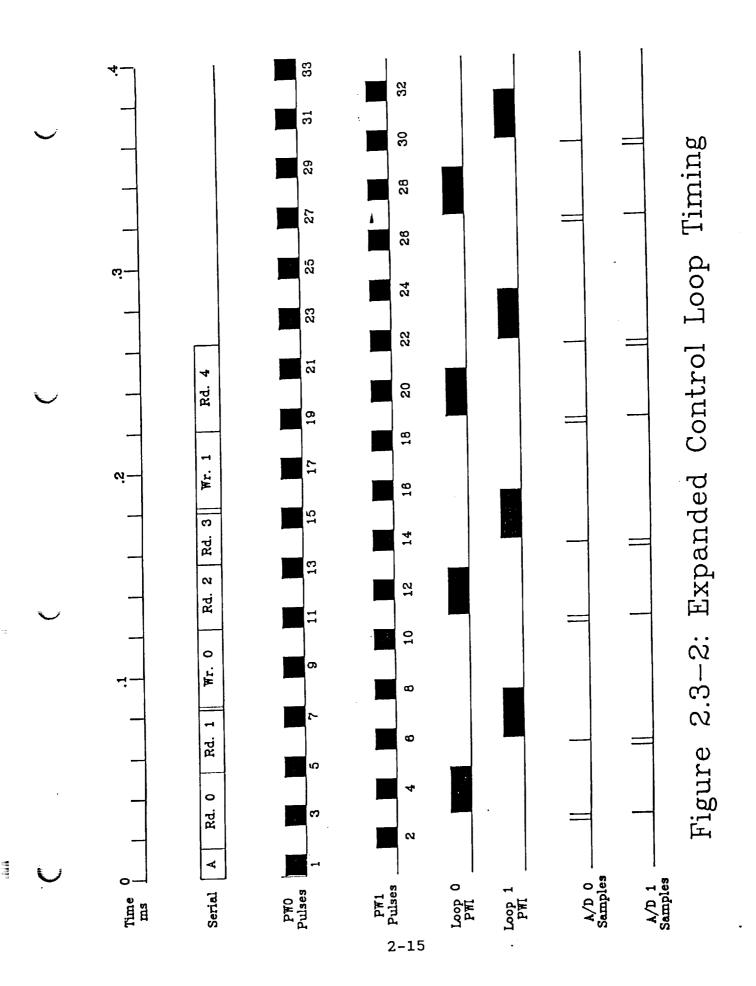

|   | 2.3 System Timing                                                                              | 2 - 12           |

|   | 2.3 System Timing                                                                              | 2 - 16           |

|   | 2.4 Output Functions                                                                           | 2 - 10<br>2 - 16 |

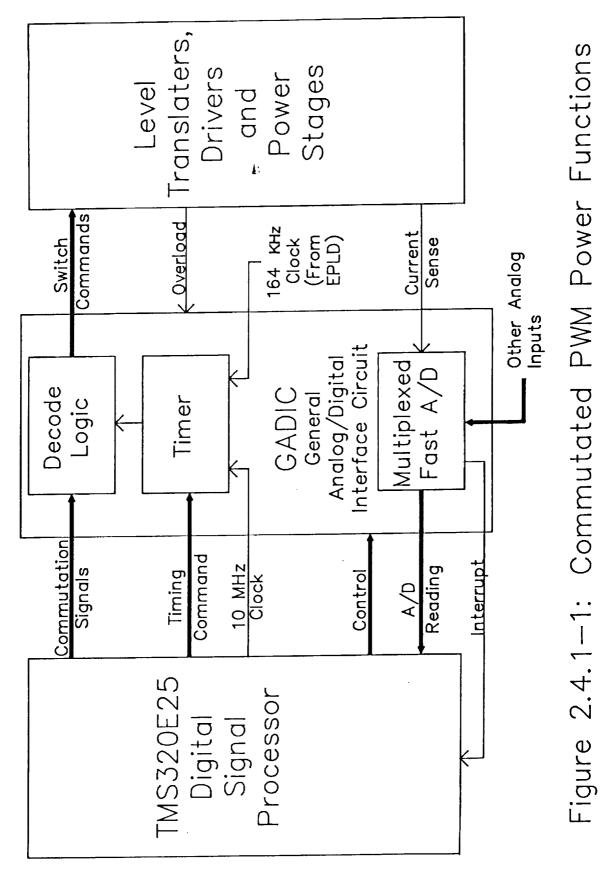

| / | 2.4.1 PWM Motor Control                                                                        | 2 - 10<br>2 - 16 |

|   | 2.4.1.1 Overall Functional Description                                                         | 2 - 10<br>2 10   |

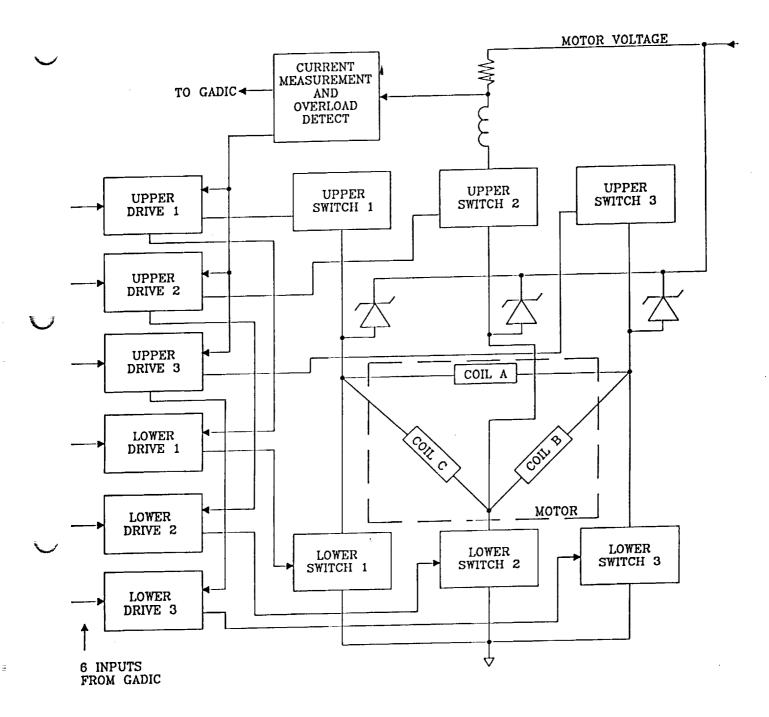

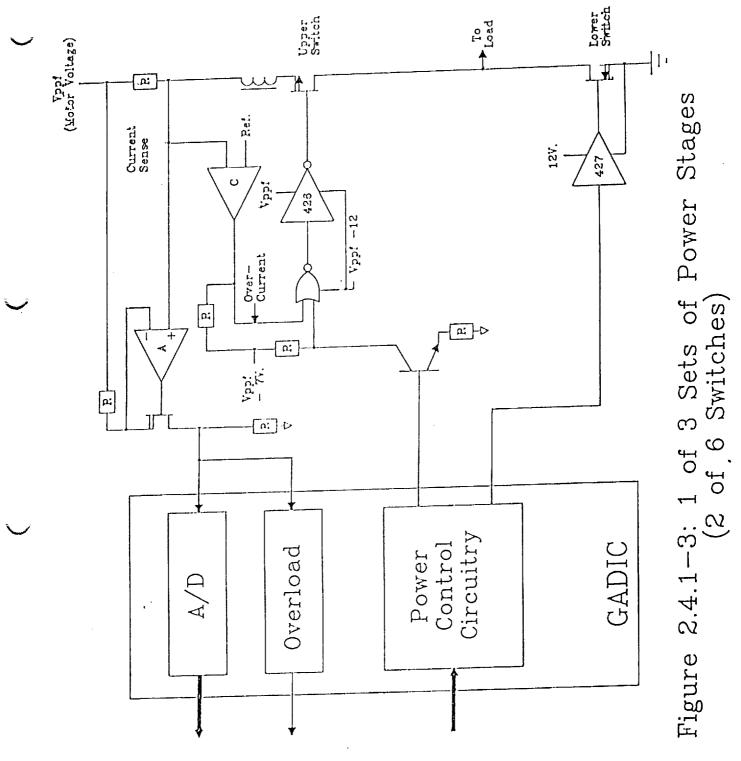

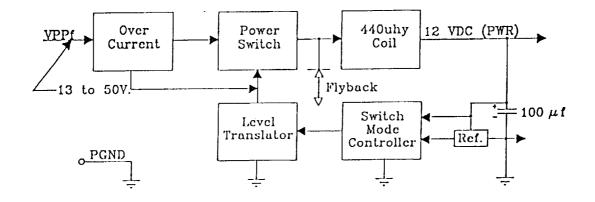

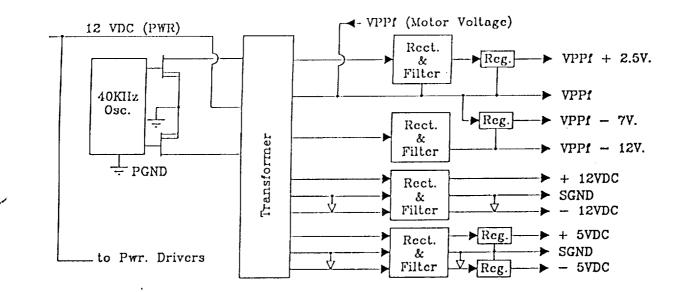

|   | 2.4.1.2 Motor Driver Amplifier Power Stage                                                     | 2-10             |

|   | 2.4.2 Other Output Functions                                                                   | 2-23             |

|   | 2.4.2.1 Power Discrete Outputs                                                                 | 2-23             |

|   | 2.4.2.2 D/A Outputs                                                                            | 2-23             |

|   | 2.4.3 Output DC Power Provisions                                                               | 2-23             |

|   | 2.5 Input Functions                                                                            | 2-24             |

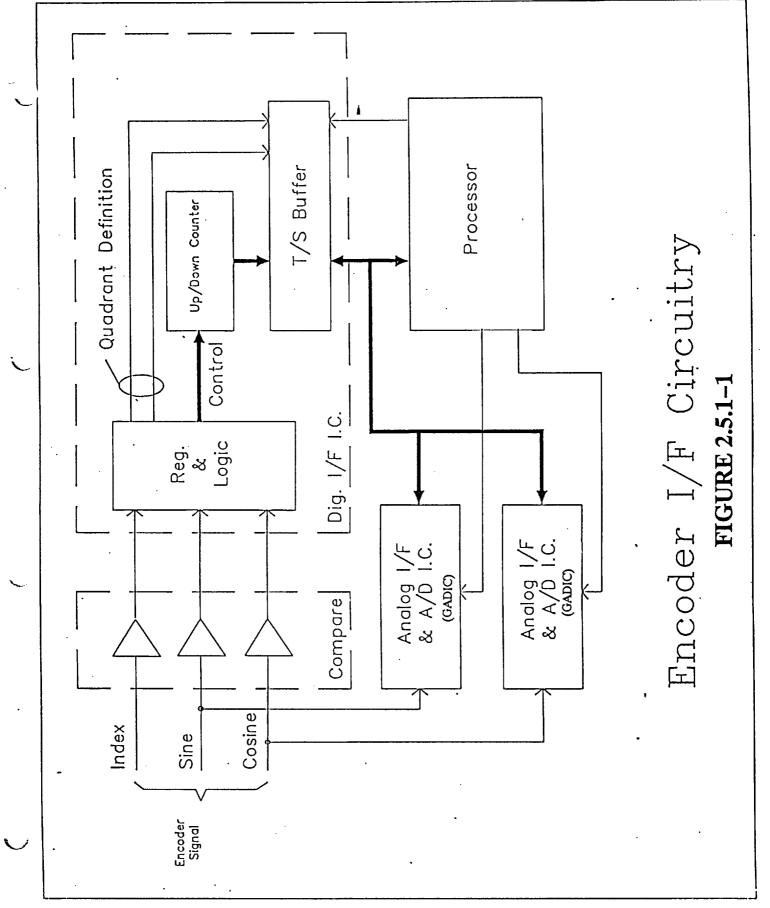

|   | 2.5.1 Incremental Encoder I/F                                                                  |                  |

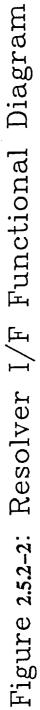

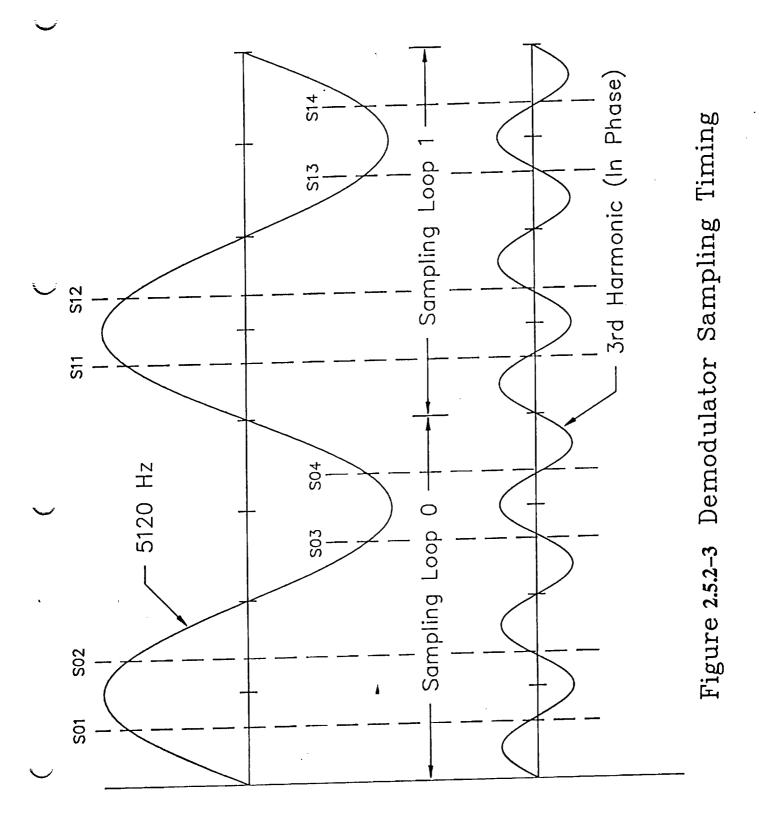

|   | 2.5.2 Resolver I/F                                                                             | 2-24             |

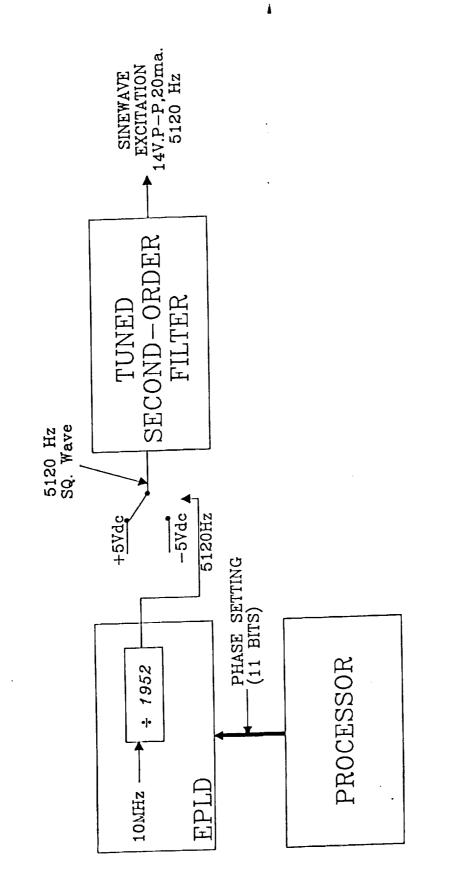

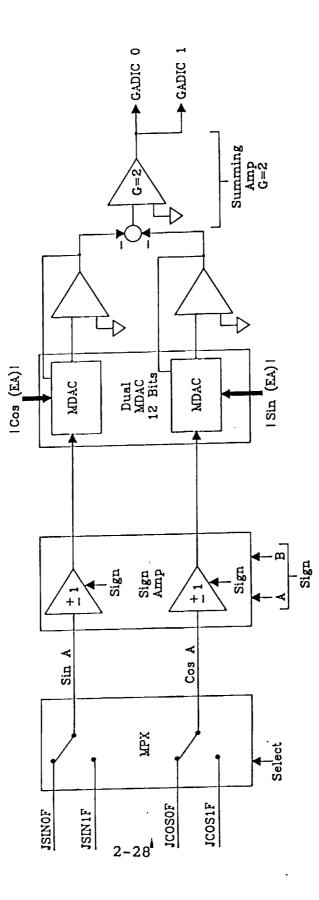

|   | 2.5.2.1 Functional Description                                                                 | 2-24             |

|   |                                                                                                | 2-29             |

|   | 2.5.3 Discrete/Absolute Encoder Inputs and Control .                                           | 2-31             |

|   | 2.5.4 High Gain Differential Inputs                                                            | 2-31             |

| ŕ | 2.5.5 Additional A/D Inputs                                                                    | 2-31             |

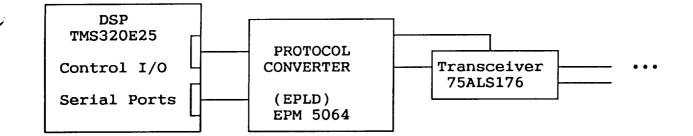

|   | 2.6 Serial I/F to DDSC Slaves                                                                  | 2-32             |

|   | 2.6.1 Introduction                                                                             | 2-32             |

|   | 2.6.2 Implementation of NAVLINK                                                                | 2-33             |

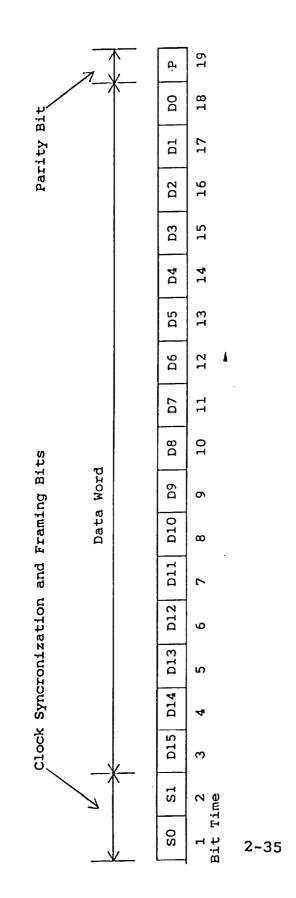

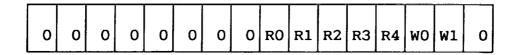

|   | 2.6.3 Serial Word Format                                                                       | 2-33             |

|   | 2.6.4 Communications Slot Format And Description                                               | 2-37             |

|   | 2.7 Master Controller/Supervisory Computer Softwar                                             | re               |

|   | Interface                                                                                      | 2-41             |

|   | Interface                                                                                      | 2-44             |

|   | 3. User's Guide for the DDSC                                                                   | 3-1              |

|   | 3.1 Hardware Interface Descriptions                                                            | 3-1              |

|   |                                                                                                |                  |

|   | 3.1.1 Description of Signals and Pinouts for the DDSC<br>3.1.2 Basic Requirements for the DDSC | 3-1              |

|   | 3.1.2 Basic Requirements for the base                                                          | 3-1              |

|   | 3.1.3 Predefined Input Capabilities                                                            | 3-9              |

|   | 5.1.4 Frederined Output Capabilities                                                           |                  |

| i | 3.1.5 Configuration of NASA GSFC's DDSC (Robotics) .                                           | 3-14             |

|   | 3.1.5.1 Description of End Effector Feedback                                                   | 3-14             |

### TABLE OF CONTENTS (Cont.)

| 3.1.5.2 Description of End Effector Control Outputs                                                          | 3-18 |

|--------------------------------------------------------------------------------------------------------------|------|

| 2.2 DDSC Software Descriptions                                                                               | 3-19 |

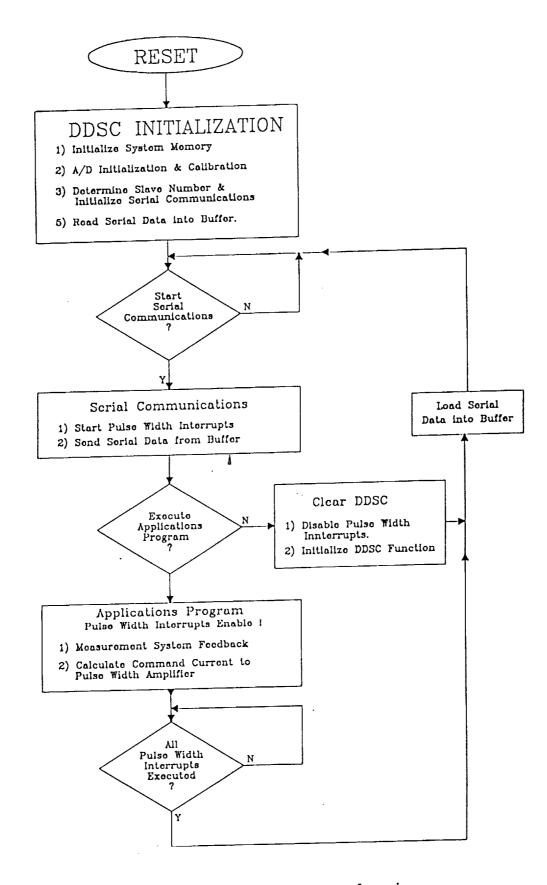

| 3.2.1 Introduction                                                                                           | 3-19 |

| 3.2.2 Program Configuration for the DDSC                                                                     | 3-19 |

| 3.2.2 Program Configuration For the DDS of the address<br>3.2.2.1 Applications Program Timing Considerations |      |

| 3.2.2.1 Applications Program Timing considerations                                                           | 3-23 |

|                                                                                                              | 3-23 |

|                                                                                                              |      |

| 3.2.3.2 DDSC Software Addresses                                                                              | 3-24 |

| J.Z.J.Z.I IIOQIQA HOMOIJ HOMOID                                                                              | 3-24 |

| 3.2.3.2.2 Data Memory Addresses                                                                              | 3-25 |

| 3.2.4 DDSC Serial Communications                                                                             | 3-27 |

| 3.2.4 DDSC Serial Communications                                                                             | ıg   |

| Considerations                                                                                               | 3-28 |

| 3.2.4.2 Array Collection Variables                                                                           | 3-30 |

| 3.2.5 DDSC Predefined Subroutines (EPROM)                                                                    | 3-31 |

| 3.2.5.1 DELAY                                                                                                | 3-31 |

| $3.2.5.2$ FIXDAT $\ldots$                                                                                    | 3-31 |

|                                                                                                              | 3-31 |

|                                                                                                              | 3-32 |

|                                                                                                              | 3-33 |

| J.L. J.I MILLOG MALCIPICHOLD I I I I I I I                                                                   |      |

| J.L.U.I.I DIIICICICICIA INCOLOR                                                                              | 3-39 |

|                                                                                                              |      |

| J.Z.U.I.J Dystem Hartipiener Severnge                                                                        | -    |

|                                                                                                              | 3-42 |

| J.Z.U.J Cullblucion options i t t t                                                                          | 3-42 |

|                                                                                                              | 3-43 |

|                                                                                                              | 3-43 |

| J.2.0.3.0 01000 connect t t t t t t                                                                          | 3-44 |

|                                                                                                              | 3-45 |

|                                                                                                              | 3-45 |

| 3.2.6.4.1 Predefined A/D Reads                                                                               | 3-45 |

| 3.2.6.4.2 General A/D Reads                                                                                  | 3-46 |

| 3.2.6.5 Utilizing A/D Measurements in the DDSC .                                                             | 3-47 |

| 3.2.7 Special Signal Inputs                                                                                  | 3-49 |

| 3.2.7.1 Analog Measurements                                                                                  | 3-49 |

| 3.2.7.2 Special Discrete                                                                                     | 3-50 |

| 3.2.7.3 Special Signal Offset Adjustment                                                                     |      |

|                                                                                                              | 3-51 |

|                                                                                                              | 3-51 |

| 5.2.6 Specialized interideed (2:22) vit vit vit                                                              | 3-53 |

|                                                                                                              | 3-53 |

|                                                                                                              |      |

|                                                                                                              | 3-55 |

| 0.2.0.1 magn odan berrentere                                                                                 | 3-56 |

|                                                                                                              | 3-56 |

|                                                                                                              | 3-57 |

|                                                                                                              | 3-59 |

| 0.21710                                                                                                      | 3-59 |

|                                                                                                              | 3-60 |

| 3.2.9.5 Timing Considerations                                                                                | 3-61 |

# TABLE OF CONTENTS (Cont.)

----

Ruth Hillard

|    | 3.2.10 Analog Output (D/A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |   |   |   | • | 3-62    |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---------|

|    | 3.2.10 Analog Output (D/A) 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |   |   |   |   | 3-62    |

|    | 3.2.10.2 Reference Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |   |   |   |   | 3-63    |

|    | 3.2.10.2 Reference Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | - | - |   |   |   | 3-64    |

|    | 3.2.11 Discrete Input / Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   | - | - | - |   | 3-65    |

|    | 3.2.11.1 Discrete Inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | • | • | • | • |   | 3-65    |

|    | 3.2.11.2 Discrete Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | • | • | • | • | • | • • • • |

|    | the second all second three second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | - |   |   |   |   | 4-1     |

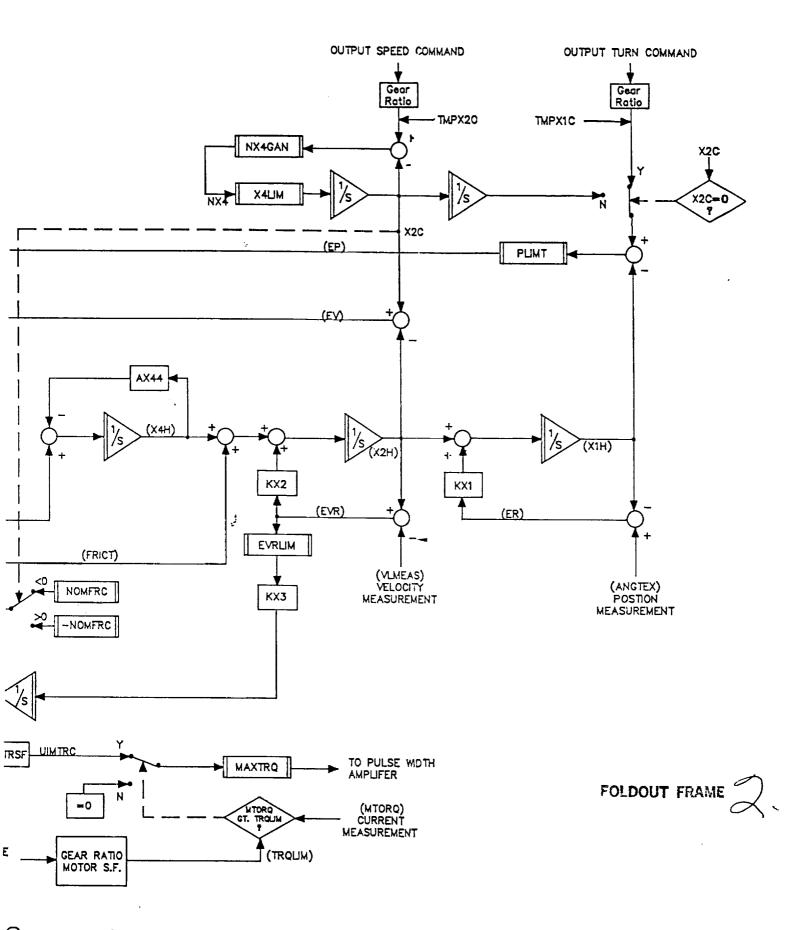

| 4. | Robotic Control Algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   | - | _ |   |   | 4-1     |

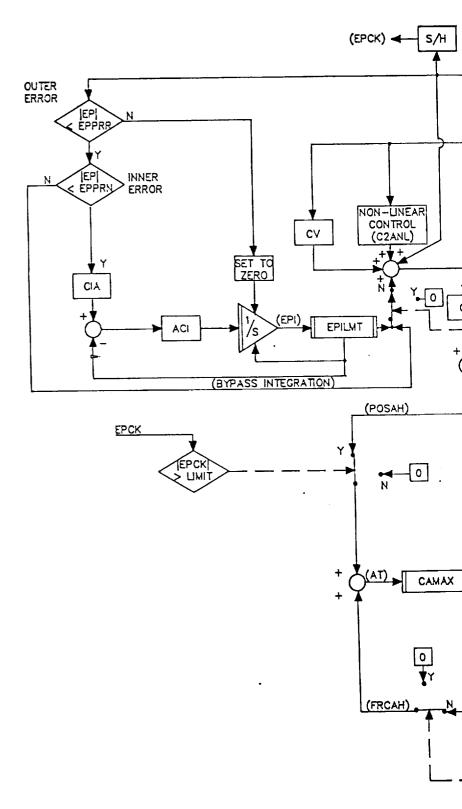

|    | 4.1 Gripper Control Algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | • | • | · | - |   | 4-1     |

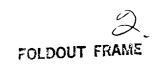

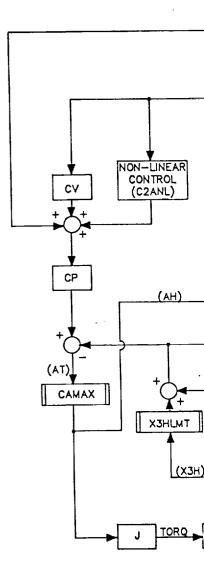

|    | 4.1.1 Position Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | • | • | • |   |   | 4-1     |

|    | 4.1.1.1 Position Feedback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | • | • | • | • | • | 4-3     |

|    | 4.1.1.2 Command Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | • | • | • | • | • | 4-3     |

|    | 4.1.1.3 Position Control Calculations .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | • | • | • | • | • | 4-5     |

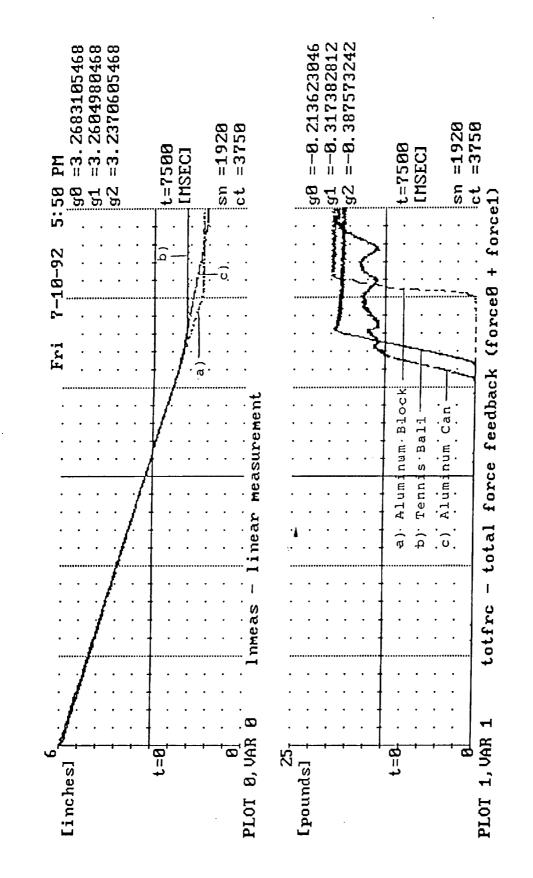

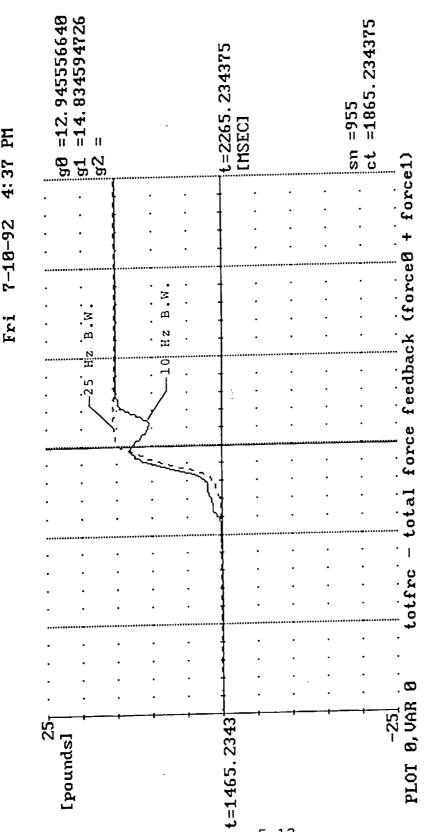

|    | 4.1.2 Force Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | • | • | • | • | • | 4-5     |

|    | 4.1.2.1 Force Feedback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | • | • | • | • | • | 4-5     |

|    | 4 1 2 2 Force Control Calculations ••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | • |   |   | • | • |         |

|    | A 1 3 Force / Position Control Switching .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | • | • | • | • | • | 4-6     |

|    | A D Materian Control Algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |   |   | • |   | 4-6     |

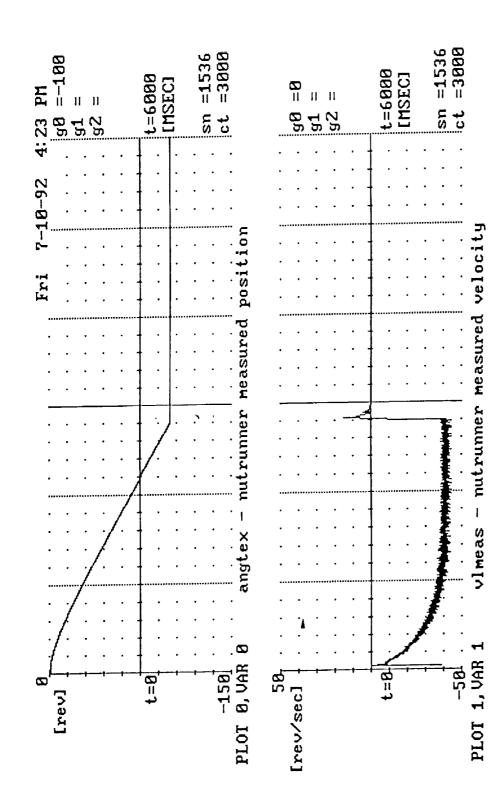

|    | 4 2 1 Nutrupper Command Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | • | • | ٠ | ٠ | • | 4-8     |

|    | 4.2.2 Nutrunner Control Algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   | ٠ | • | • | • | 4-8     |

|    | A 2 2 1 Nutrupper Feedback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | • | • |   |   | • | 4-9     |

|    | 4 2 2 2 Nutrupper Control Calculations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | • |   | • | • | 4-9     |

|    | 4.2.3 Nutrunner Output Torque Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | • | • |   |   | • | 4-10    |

|    | 4.2.5 Nutrunner Subput Torque contest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |   |   |   |   |         |

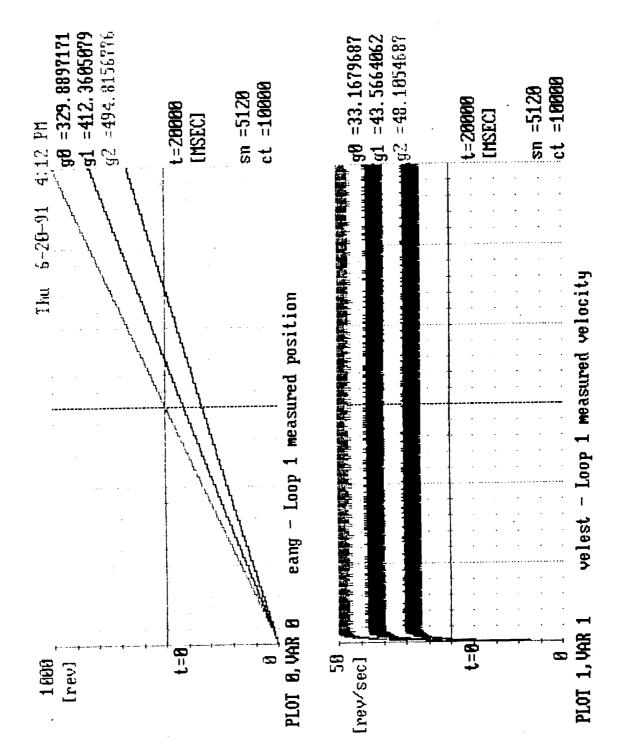

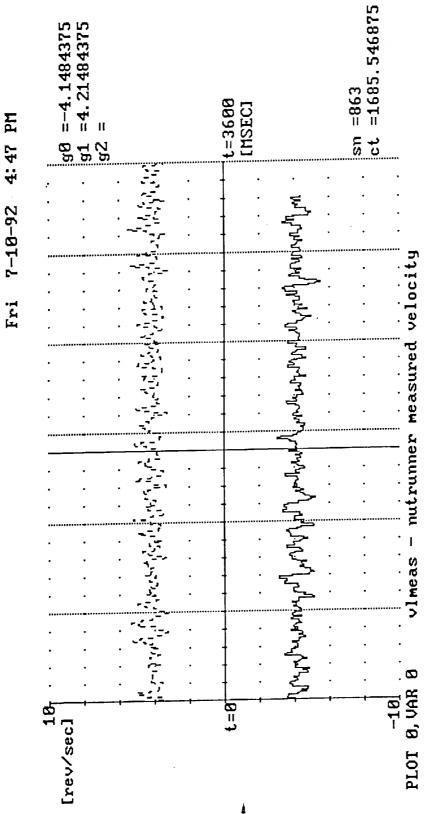

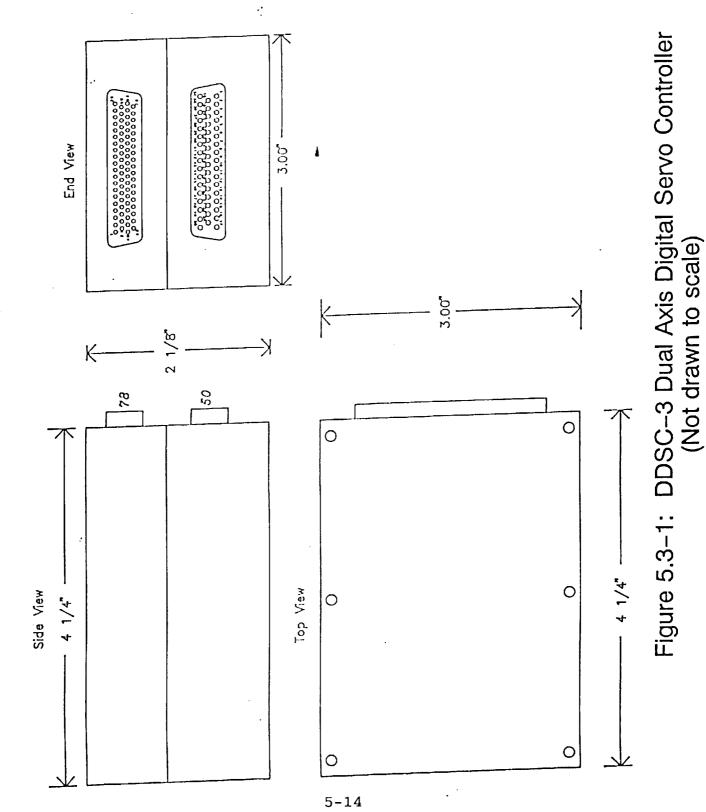

| 5  | Test Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | • | • |   | • | • | 5-1     |

| 5  | 5.1 Primary Accomplishment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |   |   | • | • | 5-1     |

|    | 5.1 Filmary Accomplishment of the second sec |   |   | • | • |   | 5-1     |

|    | 5.2 Acceptance lest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |   |   |   | • | 5-1     |

|    | 5.2.2 Current Control Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   | - | - |   |   | 5-2     |

|    | 5.2.2 Current Control lest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | • | • | • | - |   | 5-2     |