## Low Cost Arc Fault Detection and Protection for PV Systems

January 30, 2012 — September 30, 2013

Scott McCalmont *Tigo Energy, Inc. Los Gatos, California*

NREL Technical Monitor: Harin Ullal

NREL is a national laboratory of the U.S. Department of Energy Office of Energy Efficiency & Renewable Energy Operated by the Alliance for Sustainable Energy, LLC

This report is available at no cost from the National Renewable Energy Laboratory (NREL) at www.nrel.gov/publications.

Subcontract Report NREL/SR-5200-60660 October 2013

Contract No. DE-AC36-08GO28308

# **Low Cost Arc Fault Detection** and Protection for PV Systems

## January 30, 2012 — September 30, 2013

Scott McCalmont Tiao Enerav. Inc.

|                                                                                                                      | Los Gatos, California                                                                                                                                                    |  |  |

|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                                                                                      | NREL Technical Monitor: Harin Ullal<br>Prepared under Subcontract No. NEU-2-11979-03                                                                                     |  |  |

|                                                                                                                      |                                                                                                                                                                          |  |  |

|                                                                                                                      |                                                                                                                                                                          |  |  |

|                                                                                                                      |                                                                                                                                                                          |  |  |

|                                                                                                                      |                                                                                                                                                                          |  |  |

|                                                                                                                      |                                                                                                                                                                          |  |  |

|                                                                                                                      | NREL is a national laboratory of the U.S. Department of Energy<br>Office of Energy Efficiency & Renewable Energy<br>Operated by the Alliance for Sustainable Energy, LLC |  |  |

|                                                                                                                      | This report is available at no cost from the National Renewable Energy Laboratory (NREL) at www.nrel.gov/publications.                                                   |  |  |

| National Renewable Energy Laboratory<br>15013 Denver West Parkway<br>Golden, CO 80401<br>303-275-3000 • www.nrel.gov | Subcontract Report<br>NREL/SR-5200-60660<br>October 2013                                                                                                                 |  |  |

| Ğ                                                                                                                    | Contract No. DE-AC36-08GO28308                                                                                                                                           |  |  |

## This publication was reproduced from the best available copy submitted by the subcontractor and received no editorial review at NREL.

#### NOTICE

This report was prepared as an account of work sponsored by an agency of the United States government. Neither the United States government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States government or any agency thereof.

This report is available at no cost from the National Renewable Energy Laboratory (NREL) at www.nrel.gov/publications.

Available electronically at <u>http://www.osti.gov/bridge</u>

Available for a processing fee to U.S. Department of Energy and its contractors, in paper, from:

U.S. Department of Energy Office of Scientific and Technical Information P.O. Box 62 Oak Ridge, TN 37831-0062 phone: 865.576.8401 fax: 865.576.5728 email: mailto:reports@adonis.osti.gov

Available for sale to the public, in paper, from:

U.S. Department of Commerce National Technical Information Service 5285 Port Royal Road Springfield, VA 22161 phone: 800.553.6847 fax: 703.605.6900 email: <u>orders@ntis.fedworld.gov</u> online ordering: <u>http://www.ntis.gov/help/ordermethods.aspx</u>

Cover Photos: (left to right) photo by Pat Corkery, NREL 16416, photo from SunEdison, NREL 17423, photo by Pat Corkery, NREL 16560, photo by Dennis Schroeder, NREL 17613, photo by Dean Armstrong, NREL 17436, photo by Pat Corkery, NREL 17721.

Printed on paper containing at least 50% wastepaper, including 10% post consumer waste.

## **Table of Contents**

| 1  | Introduction                                 | 1   |  |  |

|----|----------------------------------------------|-----|--|--|

| 2  | Motivation                                   | 1   |  |  |

| 3  | Technical Background                         |     |  |  |

|    | 3.1 National Electrical Code                 | 3   |  |  |

|    | 3.2 UL 1699B                                 | 5   |  |  |

|    | 3.3 Arc Fault Detection                      |     |  |  |

| 4  | Objectives                                   | . 8 |  |  |

| 5  |                                              |     |  |  |

|    | 5.1 Phase 1                                  |     |  |  |

|    | 5.1.1 Prototype Arc Fault Detector           |     |  |  |

|    | 5.1.2 Technically Viable Arc Fault Detector  |     |  |  |

|    | 5.2 Phase 2                                  |     |  |  |

|    | 5.2.1 Prototype Gen 2 Arc Fault Detector     | 10  |  |  |

|    | 5.2.2 Commercially Viable Arc Fault Detector | 10  |  |  |

| 6  | Project Narrative                            | 11  |  |  |

|    | 6.1 Phase 1                                  |     |  |  |

|    | 6.2 Sandia National Laboratories             |     |  |  |

|    | 6.3 Highly Accelerated Life Testing.         | 16  |  |  |

|    | 6.4 Field Tests                              |     |  |  |

|    | 6.5 Phase 2                                  | 18  |  |  |

|    | 6.6 Arc Detection Sequence.                  | 21  |  |  |

| 7  | 1                                            |     |  |  |

| 8  |                                              |     |  |  |

| 9  | Summary                                      | 23  |  |  |

| 10 | Acknowledgements                             | 24  |  |  |

## **1** Introduction

Due to fire hazard safety concerns, the *National Electrical Code* requires arc-fault protection for the dc wiring associated with solar photovoltaic (PV) systems. In order to meet the \$1/watt goal of the DOE SunShot Initiative, arc fault protection must be provided within the context of \$0.40/watt balance of system and \$0.10/watt power electronics costs. A highly integrated arc fault detector and circuit interrupter is the best solution to address the safety needs of the industry while still allowing the lowest possible levelized cost of energy (LCOE) for both new installations and retrofit applications.

## 2 Motivation

There are several special considerations driving the development of dc arc-fault protection for PV systems<sup>1</sup>.

- Much of the dc wiring of a PV system is not contained within an overall enclosure. The string wiring (including the home run conductors) is typically clipped to the backside of the PV module frame and racking. Any fault in the conductors is not physically contained and therefore poses a greater risk to adjacent materials that may be flammable.

- Modern grid-interactive designs employ voltages as high as 600 V in the United States and 1000 V in other countries. High-voltage dc arcs are difficult to extinguish while energized.

- The modular nature of the string design means that there are a large number of connectors in the wiring between modules. Each connector is a separate point of failure.

- A traditional PV module has no means to disconnect the power source from the dc conductors. Even when the system is shut down, the conductors remain energized by the solar cells.

These characteristics of dc PV wiring provide a strong incentive for developing a solution that will automatically provide protection to property and personnel in the event of an arcing fault.

Fires started by faulty wiring in rooftop PV arrays have happened. The results of a welldocumented fire in Bakersfield, California, are shown in Figure 1. In this instance the fire department responded quickly and was able to contain the damage to a relatively small area, but the destructive potential of a PV fire is clear.

<sup>&</sup>lt;sup>1</sup> Tim Zgonena, Liang Ji, and Dave Dini, "Photovoltaic DC Arc-Fault Circuit Protection and UL Subject 1699B," Photovoltaic Module Reliability Workshop, Golden, CO, February 2011.

All images in this report are property of Tigo Energy, Inc.

Figure 1. Aftermath of a rooftop PV fire in Bakersfield, California<sup>2</sup>. Photo courtesy of Pete Jackson.

An arc fault in a PV array is a failure mechanism that can lead to a fire. Detecting and preventing arc faults eliminates a known hazard to the safe operation of a rooftop PV system. Passive techniques, such as improved design and construction practices, can play a role in eliminating arc faults, but a solution employing a device that actively and continuously detects and responds to arc faults will provide much greater protection.

### **3 Technical Background**

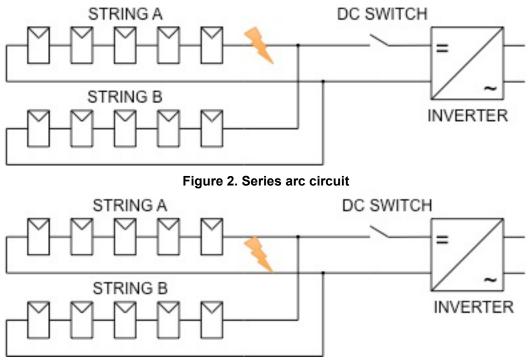

There are two types of arcs possible in the dc wiring of a PV system. A series arc is the result of the failure of the intended continuity of a conductor or connector in an electrical circuit, while a parallel arc occurs due to an unintended current path between conductors<sup>3</sup>. The impedance of the load limits the current in a series arc, as shown schematically in Figure 2. An arc fault is shown in the home run conductor for string A. The inverter determines the current in the string. If the inverter shuts off or the dc switch is opened, the string current will go to zero and the arc will be extinguished. On the other hand, the power source limits the current in a parallel arc. This is shown schematically in Figure 3, where a parallel arc occurs between the positive and negative conductors of string A. The load of the inverter actually reduces the current available to the arc. If the inverter shuts off or the dc switch opens, the current available to the arc

<sup>&</sup>lt;sup>2</sup> Pete Jackson, "Target roof PV file of 4-5-09," memo dated April 29, 2000, Development Services/Building Department, City of Bakersfield, California.

<sup>&</sup>lt;sup>3</sup> Carlos E. Restrepo, "Arc fault detection and discrimination methods," Siemens Energy and Automation, 2007. Accessed at http://w3.usa.siemens.com/powerdistribution/us/en/product-portfolio/circuit-breakers/residential-circuit-breakers/1-pole-afci/1-pole-tabs/Documents/sie-cs-cafci-2007.pdf

increases. To extinguish a parallel arc requires either shorting the string conductors to shunt the current away from the arc, or disconnecting each module from the string to remove the power source altogether.

Figure 3. Parallel arc circuit

Arc faults have been observed or reported in the internal interconnections of PV modules, in the junction boxes on the back of PV modules, and in the conductors and connectors of the dc wiring between the modules and the inverter<sup>4</sup>. Forensic analysis of PV system failures that lead to fires has shown that the overwhelming majority were caused either by series arc faults or by ground faults<sup>5</sup>. If undetected, a ground fault can contribute to a parallel arc fault, but the best way to prevent this type of failure is to improve the detection of ground faults. Because of this, the PV industry, including the relevant code and standards committees, has focused on the detection and mitigation of series arcs in PV systems.

#### 3.1 National Electrical Code

The industry's response was to add language to the *National Electrical Code* requiring series arc fault protection in rooftop PV arrays. The relevant article from the *NEC* is shown in Figure 4. Particularly noteworthy items include:

• The dc circuits must be on or penetrate a building, and operate at 80 V or more. This applies to any rooftop mounted PV array, but would also apply to a ground-mounted array if, for example, the inverter were located indoors. All modern grid-interactive PV systems operate at voltages in excess of 80 V.

<sup>&</sup>lt;sup>4</sup> Ward Bower, Scott Kuszmaul, Jay Johnson, and Jason Strauch, "Codes and standards for PV arc-fault detection and mitigation," Solar Power International, Los Angeles, California, 2010.

<sup>&</sup>lt;sup>5</sup> Greg Ball et al., "Comment on Proposal 4-246a," retrieved at http://www.solarabcs.org/codesstandards/NFPA/pdfs/2014NEC2%20690.11%204-246a.pdf on September 1, 2013.

- The arc fault protection must be listed. This means that a nationally recognized testing laboratory (NRTL) must test and certify the construction, operation, and performance of the device to a published standard.

- The detector must respond to a failure in the intended continuity of a conductor, i.e. a series arc.

- The response to the detection of an arc shall be such that the current in the affected circuit is interrupted.

- A visual indication must show that an arc was detected and the current in the circuit interrupted.

With the requirement that the detection and interruption means be listed, a standards document was needed to detail the testing required. This resulted in the development of UL 1699B, the governing document for PV arc fault protection<sup>6</sup>. The scope of UL 1699B includes dc PV arc-fault circuit protection devices intended for use in solar PV electrical energy systems, as described in Article 690 of the *NEC*. The standard covers the construction, performance, ratings, markings, and documentation associated with an arc fault device. Other UL standards are incorporated by reference in UL 1699B, including UL 1699, the standard for arc-fault circuit interrupters, and UL 1998, the standard for software in programmable components.

#### 690.11 Arc-Fault Circuit Protection (Direct Current).

Photovoltaic systems with dc source circuits, dc output circuits, or both, on or penetrating a building operating at a PV system maximum system voltage of 80 volts or greater, shall be protected by a listed (dc) arc-fault circuit interrupter, PV type, or other system components listed to provide equivalent protection. The PV arc-fault protection means shall comply with the following requirements:

- (1) The system shall detect and interrupt arcing faults resulting from a failure in the intended continuity of a conductor, connection, module, or other system component in the dc PV source and output circuits.

- (2) <sup>(2)</sup> The system shall disable or disconnect one of the following:

- (a) Inverters or charge controllers connected to the fault circuit when the fault is detected

- (b) System components within the arcing circuit

- (3) The system shall require that the disabled or disconnected equipment be manually restarted.

- (4) The system shall have an annunciator that provides a visual indication that the circuit interrupter has operated. This indication shall not reset automatically.

#### Figure 4. 2011 National Electrical Code Article 690.11<sup>7</sup>

<sup>&</sup>lt;sup>6</sup> "UL 1699B, Outline of investigation for photovoltaic (PV) dc arc-fault circuit protection, Issue number 2," Underwriters Laboratories Inc., January 14, 2013.

<sup>&</sup>lt;sup>7</sup> National Fire Protection Agency, *NFPA* 70: *National Electrical Code*, 2011.

#### 3.2 UL 1699B

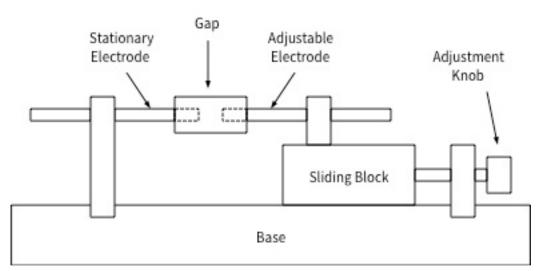

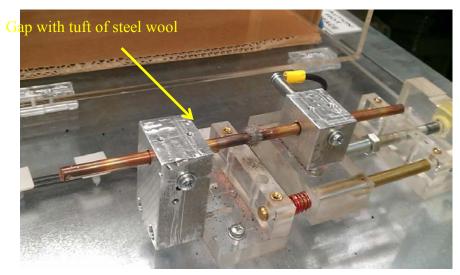

A substantial portion of UL 1699B is devoted to the tests related to the performance of the arc fault detector and circuit interrupter. For many of the tests an arc with a known voltage and current must be created using an arc generator as shown in Figure 5. The generator features two copper electrodes, one moveable and the other stationary. An adjustment knob allows the gap between the electrodes to be varied as necessary—a smaller gap corresponds to a lower power arc, while a larger gap is required for a higher power arc. A polycarbonate tube fits over the ends of the electrodes. During a test, a small tuft of steel wool is placed inside the tube between the electrodes. The steel wool bridges the gap and allows the arc current to start to flow. Once the arc is established, the steel wool melts away, similar in operation to a fuse element, allowing the arc to be established across the full air gap.

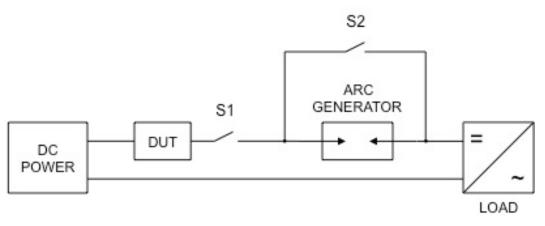

For a series arc fault detector, which is called a Type 1 device in UL 1699B, the test circuit places the arc generator in series with the device under test (DUT), as shown in Figure 6. The dc power source may be either an array of PV modules or a power supply. The load may be an inverter, as shown in the figure, or simply a resistor bank, depending upon the specific test being performed. Finally, two switches are required to initiate the test. Series switch S1 prevents the arc from starting until it is closed, and can be used for tests where current does not need to be established in the circuit prior to the formation of the arc. Shunt switch S2 bypasses the arc generator when closed, allowing the circuit to operate normally until it is opened, at which point the arc will be established.

An exhaustive list of tests required by UL 1699B is not listed here, but key tests include:

- Surge Pulses of high voltages (up to 3 kV) are applied to the input of the device, after which the device must function normally.

- Environmental The device undergoes a sequence of temperature extremes, after which it must continue to function normally.

- Arc fault detection An arc generator of specified design is used to create series arcs of different currents and powers. The detector is required to respond and interrupt the current within a period of time determined by the arc power.

- Unwanted trips The device is operated with a variety of loading conditions, including a single-phase inverter, three-phase inverter, and a charge controller. An external dc disconnect switch is also operated in an on-off sequence. No false trips may be detected.

- Operation inhibition The device must be able to detect arcs even in the presence of masking signals, including inverter switching noise, parallel strings, and different line impedances. This test requires variations of the circuit in Figure 6; for example, the line impedance test requires adding 200 feet of wire between the DUT and switch S1, to simulate the effects of the cable impedance of an array.

- Environmental noise External electromagnetic interference (EMI) must not cause the device to malfunction.

- Overload The interrupting means must not fail even when overloaded, such as by a short circuit on the PV string wiring.

- Endurance The disconnecting means must continue to operate normally after 1000 cycles at full load current.

- Withstand The device must be able to accept voltages outside the normal operating limits on the dc terminals.

- Corrosion A soak of raised temperature and humidity is applied to the device, after which it must continue to function normally.

The requirements of UL 1699B, while thorough, are primarily intended to provide an assessment that the device meets a basic level of functionality and reliability. The standard does not in any way address the means by which an arc fault detector operates. Some of the tests directly require the detection of an arc, whereas others expose the detector to some stress condition, after which it must continue to operate (and therefore successfully detect an arc).

Figure 5. Arc generator

For a Type 1 series arc detector, UL 1699B specifies that the time from when the arc is established until the DUT detects or interrupts the arc shall not be longer than 2 seconds, and for higher power arcs shall be no longer than

$$t = \frac{750 \text{ Joules}}{I \cdot V}$$

where I is the measured arc current and V is the measured arc voltage. The DUT is tested three times at the arc conditions shown in Table 1.

| Current (A) | Voltage (V) | Power (W) | Gap (in) | Time (s) |

|-------------|-------------|-----------|----------|----------|

| 7           | 43          | 300       | 1/16     | 2        |

| 7           | 71          | 500       | 3/16     | 1.5      |

| 14          | 46          | 650       | 1/8      | 1.2      |

| 14          | 64          | 900       | 1/4      | 0.8      |

Table 1 – Arc test conditions and clearing times

In their certification process, UL distinguishes between a *listed device* and a *recognized component*. A device may be installed as a separate piece of equipment in an electrical system, while a component is incomplete in construction features or restricted in performance capabilities. Typically a component is used as part of a larger piece of equipment; for example, a detector that is a recognized component might be designed into a combiner box, which is a listed device.

#### 3.3 Arc Fault Detection

There are two approaches to detecting an arc fault: the measured value of the dc current in a conductor, or the measured value of the ac current in a conductor. There are a variety of ways to measure the dc current, but the simplest is to add a small impedance in series with the circuit and measure the resultant voltage. This additional impedance represents a loss in the PV system, however, and is therefore undesirable. Measuring the dc current also assumes that there will be a detectable difference in the value without an arc and the value with an arc. In fact, since the current continues to flow through the arc, this may not be a good assumption, so measuring the dc current is not a promising technique for arc detection.

Measuring the ac current, on the other hand, is relatively easy. Because of the oscillatory nature of an ac current, a transformer may be used as the sensing element. This is commonly used for meters that measure the energy production from a PV system, where a toroidal device called a current transformer (CT) senses the current in a wire without requiring any electrical connection to the wire. In terms of a transformer, the primary coil is the single wire being measured, and the secondary coil is wrapped around the ferrous core of the transformer.

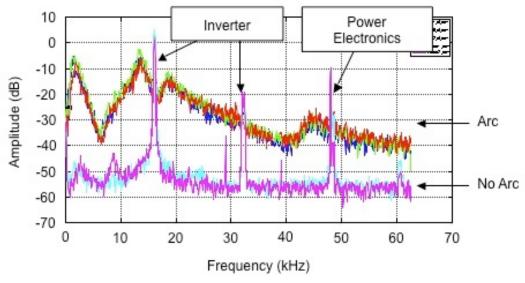

Figure 7 shows the frequency spectrum measured on the wiring of a PV system both with and without an arc present. With no arc the ac signal is generally quite small, except for several peaks that are related to the switching of the inverter and other power electronics present in the system. With an arc present a more complex spectrum is evident, with the addition of 1/f (pink) noise<sup>8</sup>. A potential detection scheme, therefore, would be to look at the ac signal on the PV wiring in the 10's to 100's of kilohertz range, and set a threshold above which an arc is presumed

<sup>&</sup>lt;sup>8</sup> Robert L. LaRocca, P.E., "Arc fault circuit interrupter requirements for PV systems," World Renewable Energy Forum, Denver, Colorado, May 16, 2012. Accessed at http://energy.sandia.gov/wp/wp-content/gallery/uploads/WREF\_Arc-Fault\_Forum\_Johnson\_SAND2012-3097C.pdf.

to be present. As Figure 7 shows, however, the peaks due to the switching of the power electronics in the PV system may be considerably larger in amplitude than the noise due to the arc. Furthermore, these peaks are not guaranteed to be located at a particular frequency, even for a specific piece of equipment, as it may operate at different frequencies depending upon the conditions present. Any detection scheme must handle these challenges and provide a robust means of reliably detecting arcs without creating nuisance trips due to other sources of noise in the system.

Figure 7. Frequency spectrum with and without arc

There are other challenges faced by the arc detector<sup>9</sup>. The wiring of PV systems is designed for carrying dc currents, not high-frequency ac signals, and is not standardized in terms of length, conductor size, or surrounding environment. The arc signature may be attenuated or amplified as it passes through the system. Antenna effects and crosstalk can further exacerbate the situation. A successful detector needs to be able to handle all of these types of effects.

### **4** Objectives

The specific objective of this 18-month research effort was to develop an off-the-shelf arc-fault detector. The starting point of the project was a prototype detector that was constructed using discrete components and laboratory equipment. An intermediate objective was to build a technically viable detector using programmable components in the detector circuitry. The final objective was to build a commercially viable detector by reducing the cost of the circuitry through the use of more sophisticated programmable components and higher levels of integration.

<sup>&</sup>lt;sup>9</sup> Jay Johnson, Scott Kuszmaul, Jason Strauch, and Ward Bower, "PV Arc Fault Detector Challenges due to Module Frequency Response Variability," 2011 PV Module Reliability Workshop, Golden, Colorado. Accessed at http://www1.eere.energy.gov/solar/pdfs/pvmrw2011\_p12\_gen\_johnson.pdf.

### **5 Milestones & Deliverables**

### 5.1 Phase 1

The starting point of this project was a laboratory prototype of an arc fault detector. This device, while suitable for testing the functionality and performance of the detector, was not practical as a commercial product due to its size and complexity. Phase 1 of the project focused on the further development of this prototype arc fault detector into a technically viable product. Key performance metrics included functionality, reliability, and low false alarm rate. A principal area of development was to improve the detection of weak arcs while also implementing the first level of integration and cost reductions necessary to transition from the laboratory prototype to a viable product. Tasks involved included hardware and software development, integration, testing, and starting pilot production.

#### 5.1.1 Prototype Arc Fault Detector

The first task in Phase 1 refined and developed the initial prototype arc fault detector technology. Milestones during this task included:

- Testing the alpha-version prototype arc fault detector for functionality and performance.

- Completing the design and layout of a new arc fault detector printed circuit board that equals the functionality and performance of the initial prototype detector.

- Building a limited number of printed circuit board assemblies of the arc fault detector.

- Designing a suitable enclosure for the printed circuit board assembly and additional components.

- Testing and demonstrating the functionality and performance of the arc fault detector.

Deliverables provided to NREL during the first task of Phase 1 included:

- A sample of the initial prototype arc fault detector, with functionality and performance meeting UL 1699B.

- Design specifications for a new arc fault detector based on the initial prototype.

- An early version of the arc fault detector printed circuit board assembly, for independent verification of its performance and functionality.

#### 5.1.2 Technically Viable Arc Fault Detector

The second task in Phase 1 brought the arc fault detector to the point where it could be sold commercially. Milestones associated with this task included:

- Completing the assembly of a small number of arc fault detectors, including the necessary enclosure and other required components.

- Testing the arc fault detector for compliance to UL 1699B.

- Performing accelerated stress testing on the arc fault detector.

- Installing the arc fault detector system at sites throughout the United States for long-term field trials.

- Establishing a U.S. production line for the arc fault detector.

- Developing and implementing a quality-control system for the production and test facility.

Deliverables provided to NREL with this task included:

- A fully assembled and functional arc fault detector that met UL 1699B. This detector was certified as a UL recognized component.

- A certified and UL listed arc fault detector, i.e. a standalone product that may be installed in new or retrofit PV applications.

### 5.2 Phase 2

Phase 2 of the project addressed cost and size reductions of the arc fault detector by using advanced circuit elements and increased integration. Key performance metrics for the Phase 2 detector were reduced size and lower power consumption.

#### 5.2.1 Prototype Gen 2 Arc Fault Detector

During the first task of Phase 2 the second-generation arc fault detector was designed and developed. Milestones associated with this task included:

- Completing an initial analysis and evaluation of the field tests from Phase 1. The results from the field tests helped inform decisions made in the design and development of the Phase 2 detector.

- Completing the design and layout of the second-generation arc fault detector.

- Completing a limited number of printed circuit board assemblies.

- Designing an enclosure for the second-generation arc fault detector.

- Testing the second-generation design for functionality and performance.

Deliverables provided to NREL during this task included:

- A UL listed device based on the UL recognized component from Phase 1.

- A report on the findings from the Phase 1 field trials.

- A functional printed circuit board assembly of the second-generation design that met UL 1699B.

#### 5.2.2 Commercially Viable Arc Fault Detector

The second task in Phase 2 further refined the second-generation arc fault detector and brought it to the point where it can be commercially successful. Milestones associated with this task included:

- Completing the assembly of a limited number of second-generation arc fault detectors, including the enclosure and other required components.

- Completing compliance and certification testing to UL 1699B.

- Completing accelerated stress tests.

- Installing the second-generation design at sites throughout the United States for long-term field trials.

- Establishing a production facility in the U.S.

- Developing and implementing a quality-control system for the production and testing of the arc fault detector.

Deliverables provided to NREL during this task included:

- A fully assembled and functional arc fault detector, including the enclosure, which met the requirements of UL 1699B.

- A UL recognized component arc fault detector.

### 6 **Project Narrative**

### 6.1 Phase 1

The starting point of the entire project was a prototype arc fault detector. The principal circuitry for this detector is shown in Figure 8. This prototype was useful for demonstrating the proof of concept, and furthermore provided a platform for developing and testing the design, but it is too complex and requires too many components to be commercially viable or successful. Figure 9 shows one of two arc generators built (one was provided to NREL as part of the first deliverable). The construction closely follows the design prescribed by UL 1699B and illustrated schematically in Figure 5. The copper electrode to the left is fixed, while the one to the right is adjustable by a knob not visible in the picture. A tuft of wool is present in the gap. To the back of the generator (behind the electrodes) the cover is visible. When an arc is established, there is considerable light of all frequencies present, including ultraviolet light. As a safety precaution, and to prevent the arc from inadvertently igniting nearby materials, the opaque cover was put in place during testing.

Figure 8. Prototype arc fault detector circuit

Figure 9. Arc generator

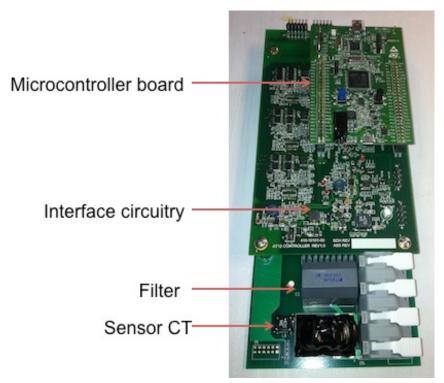

Early in Phase 1 it was determined that a design based on a microcontroller would provide the greatest flexibility for developing a robust algorithm at the lowest cost for the finished product. A suitable component was selected and a new prototype detector built. This prototype is shown in Figure 10. Note that programmable components were used in the initial discrete prototype, so much of the existing design could be ported to the new platform.

Figure 10. Microcontroller prototype arc fault detector

During this same time period a design that would be directly integrated into a PV combiner box was considered and briefly pursued. The plan was to leverage the power of the microcontroller to lower the cost of an arc fault detector suitable for up to 12 strings, by using one microcontroller to monitor the detection circuitry of more than a single string. In the end this approach was abandoned, as the additional complexity of the microcontroller interfaces required using a more expensive device than would otherwise be needed, raising the overall cost of the arc fault protection solution.

The final design chosen for the Phase 1 arc fault detector is shown in Figure 11. The enclosure is a standard electronics box, which provides a watertight design without requiring custom tooling and manufacturing. Inside the enclosure there are two main pieces: to the top in the Figure is a large dc contactor that is in series with the string wiring from the PV array; to the bottom is the printed circuit board assembly that includes the current sensor, noise filter, analog detection circuitry, and the microcontroller. The device is inserted into a PV string in series and requires a connection to both the positive and negative conductors. For best detection capabilities, the device should be placed in the string wiring between the array and the inverter.

Figure 11. Phase 1 arc fault detector

The final step in Phase 1 was to certify the arc fault detector to UL 1699B. Samples of the detector were submitted to UL for testing, and then additional tests were performed at other locations with UL witnessing the procedures. A software audit was also performed by UL to ensure the compliance of the programmable components to UL 1998. The end result was that the

arc fault detector was listed on November 13, 2012 as a recognized component meeting the requirements of UL 1699B<sup>10</sup>.

### 6.2 Sandia National Laboratories

Collaborative testing of the arc fault detector was done at Sandia National Laboratories in Albuquerque, New Mexico. Sandia's Distributed Energy Technology Laboratory (DETL) has available a wide variety of PV modules, inverters, and test equipment which made it relatively easy to test the arc fault detector with a wide variety of system configurations. In addition to a sequence of tests designed to verify the detector's functionality and performance, the detector was left installed in a test system at Sandia for a long-term field trial.

Arcs were generated in PV systems at Sandia using both an inverter and a resistive load bank as a load. It was found that generating an arc fault with the load bank was not challenging, but that generating an arc fault with an inverter could be difficult if the string length was not sufficient. It was concluded that the difficulty with shorter strings was due to the lower string voltage available with this configuration. The maximum voltage available to start the arc with the system in operation is the open-circuit voltage of the modules minus the operating voltage of the inverter just before the gap is introduced. Since the inverter's input storage capacitors will be charged to the operating voltage, the voltage available to the arc will be limited by this difference until the capacitors discharge sufficiently to allow a greater voltage to be available to the arc. This suggests that a system with shorter strings will be less likely to form an arc fault in actual operation.

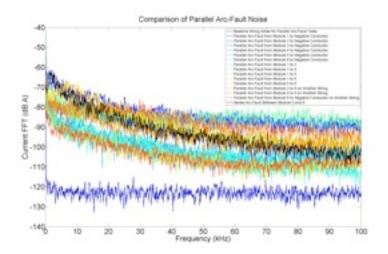

A study of the response of the arc fault detector to both serial and parallel arcs was also done with Sandia<sup>11</sup>. Although the detector developed for this project is intended to work only for series arc faults, the study with Sandia looked at how this type of system would respond when presented with a parallel arc fault. Two specific parallel fault paths were explored: the cross-string fault, where the fault current flows from the wiring in one string to the wiring in a second, parallel string; and the intra-string fault, where the current flows from one conductor in a string to another conductor in the same string.

Parallel arc fault tests were completed with both a resistive load bank and an inverter. The load bank resistance was set to a value that established the same current as would flow for the same array operating at its maximum power point. Parallel arc faults to the grounded conductor, intrastring, and cross strings were generated. The noise spectrum present on the string conductors was captured using a spectrum analyzer and a fast Fourier transform (FFT) with a Hanning window created from dc to 100 kHz. The spectra are shown in Figure 12; the blue trace at the bottom of the chart is a baseline measurement with no arc present. The series arc spectrum (black trace) is indistinguishable from the parallel arc spectra. One conclusion which may be drawn from this test is that an arc detector, whether designed to respond to series or parallel arcs, will not be able to determine which type of arc is present based upon the noise spectrum alone.

<sup>&</sup>lt;sup>10</sup> Listing may be viewed at the Online Certifications Directory at www.ul.com.

<sup>&</sup>lt;sup>11</sup> Jay Johnson, Michael Montoya, Scott McCalmont, Gil Katzir, Felipe Fuks, Justis Earle, Armando Fresquez, Sigifredo Gonzalez, and Jennifer Granata, "Differentiating series and parallel photovoltaic arc-faults," presented at the 2012 IEEE Photovoltaic Specialists Conference (Austin, Texas), Sandia Report 2012-4511C. Accessed at http://energy.sandia.gov/wp/wp-content/gallery/uploads/38thPVSC\_SeriesvParallelFaults\_SAND2012-4443C.pdf

Figure 12. Parallel and series arc fault noise spectra

A parallel arc fault establishes a second current loop in the PV system, so a portion of the current from the array is diverted from the inverter and into the fault path. Tests with the parallel arc at different places within a string of modules showed that the current and voltage at the arc were dependent on the location. These tests also showed that the resistance of an arc fault is generally much smaller than the load resistance of the inverter. In fact, during these tests it was very difficult to keep an inverter operating during a parallel arc, as the inverter would shut down when its input current was shunted away through the arc fault.

Based on the results from this study, three approaches to differentiating between a series arc and a parallel arc were proposed:

- 1. Detect both ac noise and a change in dc current or voltage. A series arc does not affect the current or voltage present at the inverter, but a drop in one or both often accompanies a parallel arc. The slope of the change is much greater than would occur due to fluctuations in irradiance.

- 2. Set the array to open-circuit conditions once the arc fault noise signature is detected. This would extinguish a series arc fault, as the current through the strings would no longer flow, but a parallel arc fault would continue to generate ac noise. A scheme such as this would need to maintain an ac path throughout the circuit while opening the dc path, because otherwise the noise signal from the parallel arc may not propagate to the detector.

- 3. Permanently connect parallel strings to provide a path for the ac signal to propagate between strings. This approach is similar to the second one above, but ensures that the ac path for the arc noise is present, allowing a parallel arc to be reliably detected.

All three approaches have the disadvantage that more advanced system-level components are required in addition to a series arc fault detector and circuit interrupter.

The final part of the study with Sandia looked at ways to extinguish a parallel arc. This is a significantly harder problem than with a series arc, which is stopped simply by opening the affected circuit. With a parallel arc, this could actually provide more energy to the arc, as the

current in the load is now available to the fault. Creating a short circuit at the array is a possible solution, but would require safely shunting large amounts of energy to ground. Once shorted, the array could not be returned to normal operation without reestablishing the conditions that created the arc in the first place, so there is no simple way to service the fault. Alternatively, the array could be shut down by disconnecting each module independently, perhaps by power electronics distributed throughout the system and integrated into the module. This would eliminate all energy available to the parallel arc, assuming that the fault path is external to the module. The only place where an arc could persist would be within the wiring internal to the module, but this wiring is contained and assembled in a factory, and thus not nearly as susceptible to the conditions necessary for arc formation. The energy available within a PV module is relatively small, too, so an arc is not as likely to form.

### 6.3 Highly Accelerated Life Testing

Highly accelerated life testing (HALT) is performed to uncover latent defects in product design, component selection, and/or manufacturing that would not otherwise be found through conventional qualification methods. The process subjects the test product to progressively higher stress levels, incorporating thermal dwells, rapid temperature transitions, vibration, and a combination of temperature and vibration to precipitate inherent defects. Moreover, HALT stresses the product to failure in order to assess design robustness and margin above its intended operation.

The HALT sequence included the following:

- Cold thermal testing—the units were verified to operate at  $-50^{\circ}$ C.

- Hot thermal testing—the units were verified to operate at +90°C.

- Rapid thermal transitions—the units were exposed to two rapid temperature cycles from -50°C to +90°C at a transition rate of 60°C per minute. The units were verified to operate during the transitions.

- Vibration step stress—the units were subjected to a vibration step test to 30 Grms and verified to continue to operate.

- Combined environment—the units were exposed to 5 rapid thermal transitions combined with vibration ranging from 6 Grms to 30 Grms. The dwell time at each extreme was 10 minutes. The units were verified to operate throughout the process.

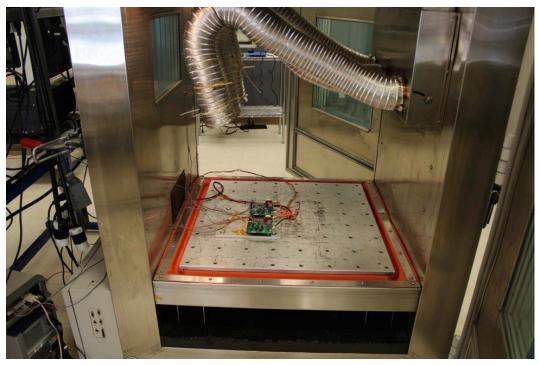

The HALT chamber setup is shown in Figure 13.

Figure 13. HALT chamber setup

The accelerated life testing was limited to only the detector printed circuit board assembly, because the large dc contactor in the complete device would not be likely to survive the severe vibration tests. Nevertheless, the testing showed several areas where the assembly of the unit could be improved, notably around the anchoring of the larger components, and these discoveries were useful in improving the design of the detector, particularly in Phase 2.

#### 6.4 Field Tests

Field tests of the arc fault detector were established at five locations: Los Gatos, California; San Jose, California; Albuquerque, New Mexico; Golden, Colorado; and Cocoa, Florida. The New Mexico, Colorado, and Florida sites in particular were eagerly anticipated as a means to evaluate the performance of the arc fault detector in the presence of lightning. Lightning is essentially a very high-energy arc between the sky and earth, and since a PV array appears as a capacitance to ground there was concern that enough noise would couple into the array to create a nuisance trip. Florida measures among the highest flash densities of cloud-to-ground lightning in the United States, so it is an excellent location for such a test. Figure 14 shows the field test unit during installation at a residential array in Florida. The arc fault detector is the box to the left. The box on the right is a junction box associated with the string wiring.

Figure 14. Field trial installation in Florida

Each of the field test locations was fitted with a datalogger and a network connection so that the data regarding any detection activity could be recorded and observed remotely. After nearly a year of operation, no unexplained nuisance trip has been recorded.

### 6.5 Phase 2

Obtaining a UL listed device based on the UL recognized component from Phase 1 was the first deliverable of Phase 2. This required adding an enclosure suitable for standalone installation and incorporating a power supply for the detection circuitry. The design submitted to UL is shown in Figure 15. Note that the same arc fault detector printed circuit board assembly (top left) and dc disconnect contactor (top right) are used, but a new ac power supply (blue, bottom left) and terminal blocks for interconnecting wires (bottom center) have been added. The enclosure is also new and much larger than what was used for the component from Phase 1. Not shown in this picture is a protective acrylic plate that prevents contact with the high voltage parts inside the box and the reset/test switch.

Figure 15. UL device construction detail

Because the device was built using UL recognized components, including the Phase 1 arc fault detector, the UL testing was simplified. On July 4, 2013, the device was approved as a listed device<sup>12</sup>.

The major design challenge for Phase 2 was to reduce the size and cost of the detector. The biggest impediment to a smaller detector was the current sensor, which must be relatively large to accommodate the string currents and conductor sizes present in PV arrays. Rather then letting this drive the size of the detector's enclosure, it was decided to move the sensor off of the printed circuit board assembly and to use a pass-through design. With this approach, the sensor does not make electrical contact with the dc conductor but couples the noise into the detector inductively. This not only allows the detector enclosure to be much smaller, but also eliminates the high voltage connection to the string wiring, improving safety easing the layout requirements of the printed circuit board. With all this in mind, a DIN rail enclosure was selected for the detector, as shown in Figure 16.

<sup>&</sup>lt;sup>12</sup> Listing may be viewed at the Online Certifications Directory at www.ul.com.

Figure 16. DIN rail enclosure

An early prototype of the pass-through current sensor is shown in Figure 17. The red and black wires carry the primary current. One advantage of the pass-through design is that simply putting more than one wire through the sensor will protect more than one string. The secondary windings are around a ferrous core and connected to the white cable. In the final design, the entire sensor would include potting or some similar protective means.

Figure 17. Pass-through current sensor

Otherwise, the workflow of Phase 2 closely followed that of Phase 1. The completed design was submitted to UL for testing to UL 1699B. All of the testing has been successfully completed, and listing of a recognized component is pending. Accelerated life tests and field trials are not complete at the time of this report.

#### 6.6 Arc Detection Sequence

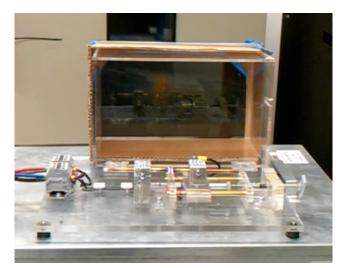

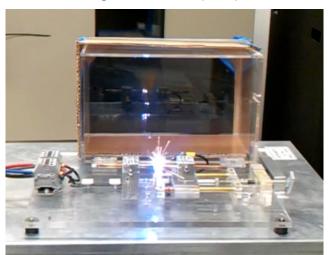

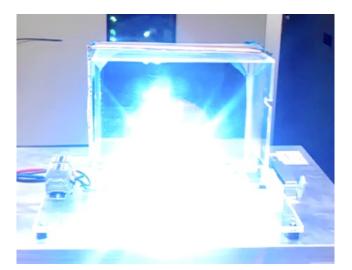

To fully appreciate the power of a dc arc from a PV array and the importance of arc fault detection requires witnessing an arc fault first hand. Given that this is impossible to convey in a written report, a sequence of images taken from a movie are included here. The setup is the laboratory arc generator. An arc is started, detected, and extinguished within a timespan of less than one second. Even this short amount of time is sufficient to gain some insight into the danger of an undetected arc fault.

Figure 18. No arc (0 ms)

Figure 19. Arc starts (33 ms)

Figure 20. Arc at full power (66 ms)

Figure 21. Detector has tripped and arc starts to decay (300 ms)

Figure 22. Arc nearly extinguished (600 ms)

This report is available at no cost from the National Renewable Energy Laboratory (NREL) at www.nrel.gov/publications.

## 7 Future Work

To fully protect PV arrays from arc fault hazards, suitable technology must be developed to detect and mitigate arc faults of all types. The work presented here provides protection from series arcs, but the industry should press forward and develop protection from parallel arcs as well. This will likely require a more complex system, and may very well best be solved at the module level, so that the energy in the PV array can be shut off at the source and eliminate all current in the string wiring between the modules and the inverter. This will provide the best protection for the system at the lowest cost.

### 8 Publications and Presentations

The following publications and presentations were made as part of this project:

- 4. Scott McCalmont, "Module-level electronics and arc fault protection," 2012 World Renewable Energy Forum, Denver, Colorado, 16 May 2012.

- 5. Jay Johnson, Michael Montoya, Scott McCalmont, Gil Katzir, Felipe Fuks, Justis Earle, Armando Fresquez, Sigifredo Gonzalez, and Jennifer Granata, "Differentiating series and parallel photovoltaic arc-faults," *38th IEEE Photovoltaic Specialists Conference (PVSC)*, p. 720–726, 3-8 June 2012.

- 6. Scott McCalmont, Gil Katzir, and Felipe Fuks, "Low-cost arc-fault detection and protection for PV systems," *DOE SunShot Grand Challenge: Summit and Technology Forum*, Denver, Colorado, 13–14 June 2012.

- 7. Scott McCalmont, "Low-cost arc-fault detection and protection," *DOE SunShot Incubator Showcase*, Oakland, California, 30 May 2013.

- 8. Scott McCalmont, "Low-cost arc-fault detection and protection," *DOE SunShot Incubator Showcase*, Boston, Massachusetts, 26 June 2013.

### 9 Summary

A low-cost arc fault detection and protection system for series arc faults in the dc wiring of photovoltaic arrays has been developed. This technology, which is mandated by the *National Electrical Code*, ensures the continued safe adoption of clean, renewable solar photovoltaic energy.

The biggest concern with the incorporation of a new technology, such as arc fault detection and protection in PV arrays, is that the immature products will be prone to nuisance trips or alerts. The best strategy to address this concern and to minimize the number of false trips is to thoroughly test the technology under a variety of conditions. Laboratory testing played a major role in this regard, but laboratory tests generally only address conditions that are anticipated—the known knowns—and not those that are not anticipated—the unknown unknowns. The collaboration with Sandia National Laboratories was very helpful in identifying conditions that created nuisance trips, leading to improvements in the detection algorithm. The field trials provide further margin for concluding that the design is robust and not subject to false trips.

### **10Acknowledgements**

Many people have contributed to the success of this project; really too many to name individually. At times it seems like nearly everyone at Tigo Energy was involved in the project, so a big thank you to all. A debt of gratitude is owed to the folks at NREL, particularly Rick Mitchell, Harin Ullal, and John Wohlgemuth. Jay Johnson of Sandia National Laboratories not only provided much help but also was also willing to debate the finer technical merits of different arc detection strategies. Bob Reedy of the Florida Solar Energy Center gave night and weekend tech support for the field trial in his jurisdiction. Finally, a special thank you to the U.S. Department of Energy, especially Victor Kane and Garrett Nilsen, for their consistent support throughout.