# NBS SPECIAL PUBLICATION 400-8

U.S. DEPARTMENT OF COMMERCE / National Bureau of Standards

# Semiconductor Measurement Technology

Quarterly Report April 1 to June 30, 1974

QC 00 157 3.400-8 975

#### NATIONAL BUREAU OF STANDARDS

The National Bureau of Standards was established by an act of Congress March 3, 1901. The Bureau's overall goal is to strengthen and advance the Nation's science and technology and facilitate their effective application for public benefit. To this end, the Bureau conducts research and provides; (1) a basis for the Nation's physical measurement system, (2) scientific and technological services for industry and government, (3) a technical basis for equity in trade, and (4) technical services to promote public safety. The Bureau consists of the Institute for Basic Standards, the Institute for Materials Research, the Institute for Applied Technology, the Institute for Computer Sciences and Technology, and the Office for Information Programs.

THE INSTITUTE FOR BASIC STANDARDS provides the central basis within the United States of a complete and consistent system of physical measurement; coordinates that system with measurement systems of other nations; and furnishes essential services leading to accurate and uniform physical measurements throughout the Nation's scientific community, industry, and commerce. The Institute consists of a Center for Radiation Research, an Office of Measurement Services and the following divisions:

Applied Mathematics — Electricity — Mechanics — Heat — Optical Physics — Nuclear Sciences 2 — Applied Radiation 2 — Quantum Electronics 3 — Electromagnetics 3 — Time and Frequency 3 — Laboratory Astrophysics 3 — Cryogenics 3.

THE INSTITUTE FOR MATERIALS RESEARCH conducts materials research leading to improved methods of measurement, standards, and data on the properties of well-characterized materials needed by industry, commerce, educational institutions, and Government; provides advisory and research services to other Government agencies; and develops, produces, and distributes standard reference materials. The Institute consists of the Office of Standard Reference Materials and the following divisions:

Analytical Chemistry — Polymers — Metallurgy — Inorganic Materials — Reactor Radiation — Physical Chemistry.

THE INSTITUTE FOR APPLIED TECHNOLOGY provides technical services to promote the use of available technology and to facilitate technological innovation in industry and Government; cooperates with public and private organizations leading to the development of technological standards (including mandatory safety standards), codes and methods of test; and provides technical advice and services to Government agencies upon request. The Institute consists of a Center for Building Technology and the following divisions and offices:

Engineering and Product Standards — Weights and Measures — Invention and Innovation — Product Evaluation Technology — Electronic Technology — Technical Analysis — Measurement Engineering — Structures, Materials, and Life Safety — Building Environment ' — Technical Evaluation and Application ' — Fire Technology.

THE INSTITUTE FOR COMPUTER SCIENCES AND TECHNOLOGY conducts research and provides technical services designed to aid Government agencies in improving cost effectiveness in the conduct of their programs through the selection, acquisition, and effective utilization of automatic data processing equipment; and serves as the principal focus within the executive branch for the development of Federal standards for automatic data processing equipment, techniques, and computer languages. The Institute consists of the following divisions:

Computer Services — Systems and Software — Computer Systems Engineering — Information Technology.

THE OFFICE FOR INFORMATION PROGRAMS promotes optimum dissemination and accessibility of scientific information generated within NBS and other agencies of the Federal Government; promotes the development of the National Standard Reference Data System and a system of information analysis centers dealing with the broader aspects of the National Measurement System; provides appropriate services to ensure that the NBS staff has optimum accessibility to the scientific information of the world. The Office consists of the following organizational units:

Office of Standard Reference Data — Office of Information Activities — Office of Technical Publications — Library — Office of International Relations.

<sup>&</sup>lt;sup>1</sup> Headquarters and Laboratories at Gaithersburg, Maryland, unless otherwise noted; mailing address Washington, D.C. 20234.

<sup>&</sup>lt;sup>3</sup> Part of the Center for Radiation Research.

Located at Boulder, Colorado 80302.

Part of the Center for Building Technology.

14 13/5 acc.

# **Semiconductor Measurement Technology**

Quarterly Report, April 1 to June 30, 1974

W. Murray Bullis, Editor

Electronic Technology Division Institute for Applied Technology National Bureau of Standards Washington, D.C. 20234

tispecial publication no 400-8

Jointly Supported by: The National Bureau of Standards, The Defense Nuclear Agency, and The Defense Advanced Research Projects Agency

U.S. DEPARTMENT OF COMMERCE, Frederick B. Dent, Secretary NATIONAL BUREAU OF STANDARDS, Richard W. Roberts, Director Issued February 1975

National Bureau of Standards Special Publication 400-8

Nat. Bur. Stand. (U.S.), Spec. Publ. 400-8, 70 pages (Feb. 1975)

CODEN: XNBSAV

U.S. GOVERNMENT PRINTING OFFICE WASHINGTON: 1975

# TABLE OF CONTENTS

### SEMICONDUCTOR MEASUREMENT TECHNOLOGY

|                                    |                                                       | PAGE                     |

|------------------------------------|-------------------------------------------------------|--------------------------|

| Prefa                              | ace                                                   | vi                       |

| 1.                                 | Introduction                                          | 1                        |

| 2.                                 | Highlights                                            | 3                        |

| 3.<br>3.1.<br>3.2.<br>3.3.<br>3.4. | Resistivity; Dopant Profiles                          | 7<br>7<br>10<br>14<br>14 |

| 4.<br>4.1.                         | Crystal Defects and Contaminants                      | 18<br>18                 |

| 5.<br>5.1.<br>5.2.                 | Oxide Film Characterization                           | 21<br>21<br>25<br>26     |

| 6.1.                               | Charge-Coupled Device Test Pattern                    | 26                       |

| 7.<br>7.1.<br>7.2.<br>7.3.         | Photolithography                                      | 28<br>28<br>29<br>30     |

| 8.<br>8.1.                         | Epitaxial Layer Thickness                             | 32<br>32                 |

| 9.<br>9.1.<br>9.2.                 | Wafer Inspection and Test                             | 34<br>34<br>36           |

| 10.<br>10.1                        | Interconnection Bonding                               | 37<br>37                 |

| 11.<br>11.1<br>11.2<br>11.3        | . Mass Spectrometer Application                       | 40<br>40<br>40<br>42     |

| 12.<br>12.1<br>12.2<br>12.3        | . Thermal Resistance Methods — Power Transistors      | 43<br>43<br>46<br>49     |

| 13.                                | References                                            | 52                       |

| Appe                               | ndix A. Semiconductor Technology Program Staff        | 55                       |

| Appe                               | ndix B. Semiconductor Technology Program Publications | 56                       |

| Appe                               | ndix C. Workshop and Symposium Schedule               | 58                       |

| Appe                               | ndix D. Standards Committee Activities                | 59                       |

| Appe                               | ndix E. Solid-State Technology & Fabrication Services | 61                       |

| Inde:                              | x                                                     | 62                       |

# LIST OF FIGURES

|     |                                                                                                                                                      | Р | AGE |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|

| 1.  | Spreading resistance of a 10 $\Omega$ -cm $p$ -type silicon specimen bevel polished with silica aquasol                                              | • | 8   |

| 2.  | Ratio of spreading resistance to four-probe resistivity for $p$ -type silicon wafers polished with silica aquasol                                    |   | 8   |

| 3.  | Radial resistivity profile of a 10 $\Omega$ cm $p$ -type silicon wafer polished with silica aquasol                                                  |   | 9   |

| 4.  | Wafer map of average dopant density derived from capacitance-voltage measurements                                                                    |   | 11  |

| 5.  | Apparent dopant density determined from capacitance-voltage measurements with and without application of the peripheral correction                   |   | 13  |

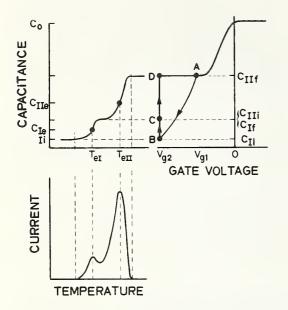

| 6.  | Capacitance-voltage characteristic and dynathermal current and capacitance response of an ideal, gold-doped $n\text{-MOS}$ capacitor                 |   | 20  |

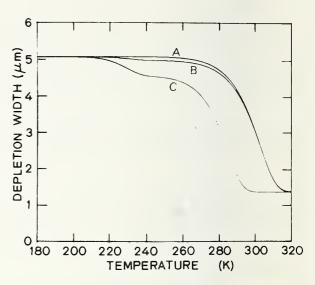

| 7.  | Calculated depletion width of a gold-doped silicon n-MOS capacitor during dynathermal response measurements                                          |   | 20  |

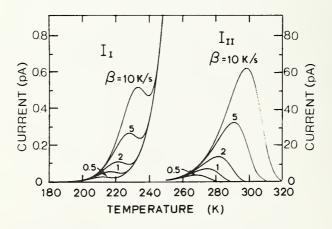

| 8.  | Calculated phase I and phase II dynathermal current response to gold acceptors in a silicon $n	ext{-MOS}$ capacitor for various heating rates        |   | 20  |

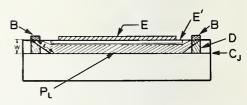

| 9.  | Representations of an MOS capacitor in the low frequency approximation                                                                               |   | 22  |

| 10. | Effect of temperature on properties of a $p	ext{-MOS}$ capacitor                                                                                     |   | 22  |

| 11. | Equivalent circuit used for the analysis of the conductance technique                                                                                |   | 22  |

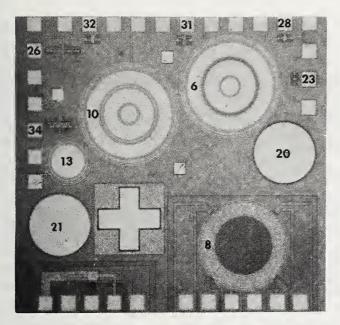

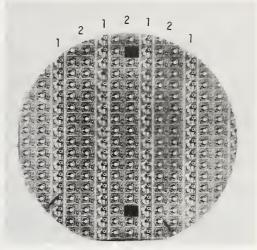

| 12. | Photomicrographs of the CCD test pattern                                                                                                             |   | 27  |

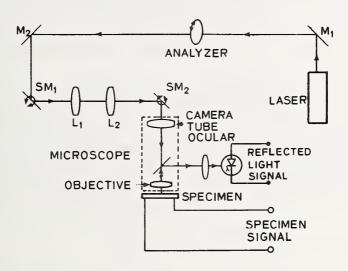

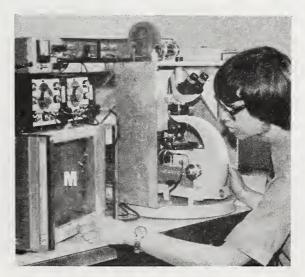

| 13. | Flying-spot scanner                                                                                                                                  |   | 35  |

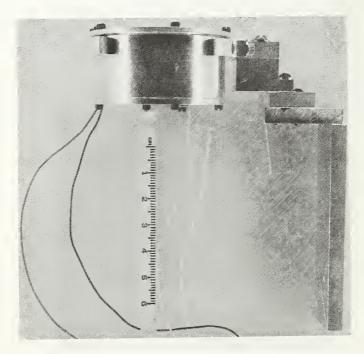

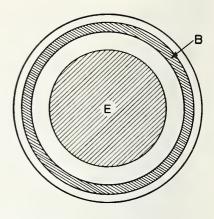

| 14. | Cylindrical secondary electron detector with mounting bracket for use with the eucentric stage of the scanning electron microscope                   | • | 36  |

| 15. | Measured and calculated normalized vibration amplitudes of ultrasonic bonding tools                                                                  |   | 38  |

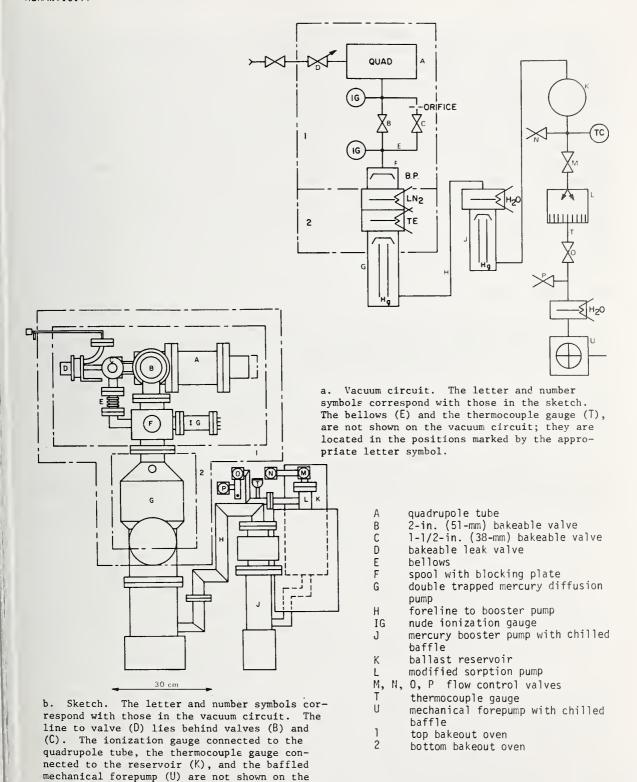

| 16. | Quadrupole mass analyzer system                                                                                                                      |   | 41  |

| 17. | Temperature-voltage curves for a hypothetical collector-base junction under operating and calibration conditions for the same total junction current |   | 44  |

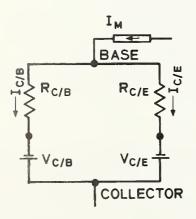

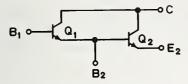

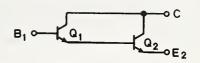

| 18. | Diagrams of transistor showing current paths for overlap diode model                                                                                 |   | 44  |

| 19. | Equivalent circuit for analysis of collector-base voltage in overlap diode model                                                                     |   | 44  |

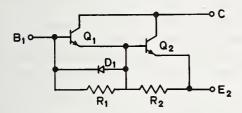

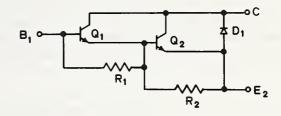

| 20. | Commercially available Darlington circuits                                                                                                           |   | 47  |

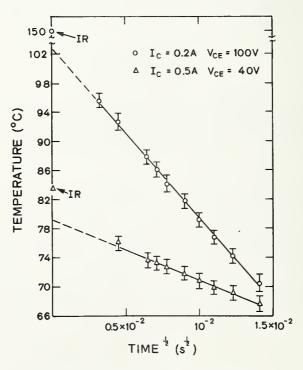

| 21. | Measured cooling response of a power transistor                                                                                                      |   | 50  |

# LIST OF TABLES

|     |                                                                                                    |   | PAGE |

|-----|----------------------------------------------------------------------------------------------------|---|------|

| 1.  | Dopant Density Profiles from Capacitance-Voltage Measurements                                      |   | 11   |

| 2.  | Ratio of Peripheral Capacitance to Measured Capacitance                                            |   | 13   |

| 3.  | Dopant Density from Capacitance-Voltage Measurements Taken and Analyzed in Different Ways          |   | 13   |

| 4.  | Analysis of Two-Probe Resistivity Round Robin                                                      | • | 16   |

| 5.  | Flame Spectrometer Analysis for Sodium Contamination                                               | • | 25   |

| 6.  | Epitaxial Layer Thickness                                                                          |   | 32   |

| 7.  | Tool Properties                                                                                    | • | 39   |

| 8.  | Calibration Curves for a Darlington Circuit                                                        |   | 47   |

| 9.  | Comparison of Electrical and Infrared Measurements of Thermal Resistance on Two Darlington Devices |   | 47   |

| 10. | Peak Temperature Cooling Curve Data                                                                |   | 50   |

| 11. | Average Temperature Cooling Curve Data                                                             |   | 50   |

#### PREFACE

The Semiconductor Technology Program serves to focus NBS efforts to enhance the performance, interchangeability, and reliability of discrete semiconductor devices and integrated circuits through improvements in measurement technology for use in specifying materials and devices in national and international commerce and for use by industry in controlling device fabrication processes. Its major thrusts are the development of carefully evaluated and well documented test procedures and associated technology and the dissemination of such information to the electronics community. Application of the output by industry will contribute to higher yields, lower cost, and higher reliability of semiconductor devices. The output provides a common basis for the purchase specifications of government agencies which will lead to greater economy in government procurement. In addition, improved measurement technology will provide a basis for controlled improvements in fabrication processes and in essential device characteristics.

The Program receives direct financial support principally from three major sponsors: the Defense Advanced Research Projects Agency (ARPA),\* the Defense Nuclear Agency (DNA),† and the National Bureau of Standards (NBS).\* The ARPA-supported portion of the Program, Advancement of Reliability, Processing, and Automation for Integrated Circuits with the National Bureau of Standards (ARPA/IC/NBS), addresses critical Defense Department problems in the yield, reliability, and availability of integrated circuits. The DNA-supported portion of the Program emphasizes aspects of the work which relate to radiation response of electron devices for use in military systems. There is considerable overlap between the interests of DNA and ARPA. Measurement oriented activity appropriate to the mission of NBS is a critical element in the achievement of the objectives of both other agencies.

Essential assistance to the Program is also received from the semiconductor industry through cooperative experiments and technical exchanges. NBS interacts with industrial users and suppliers of semiconductor devices through participation in standardizing organizations; through direct consultations with device and material suppliers, government agencies, and other users; and through periodically scheduled symposia and workshops. In addition, progress reports, such as this one, are regularly prepared for issuance in the NBS Special Publication 400 sub-series. More detailed reports such as state-of-the-art reviews, literature compilations, and summaries of technical efforts conducted within the Program are issued as these activities are completed. Reports of this type which are published by NBS also appear in the Special Publication 400 sub-series. Announcements of availability of all publications in this sub-series are sent by the Government Printing Office to those who have requested this service. A request form for this purpose may be found at the end of this report.

<sup>\*</sup> Through ARPA Order 2397, Program Code 4D10 (NBS Cost Center 4259555).

<sup>†</sup> Through Inter-Agency Cost Reimbursement Order 74-811 (NBS Cost Center 4259522).

x Through Scientific and Technical Research Services Cost Centers 4251126, 4252128, and 4254115.

# SEMICONDUCTOR MEASUREMENT TECHNOLOGY

#### QUARTERLY REPORT April 1 to June 30, 1974

Abstract: This quarterly progress report describes NBS activities directed toward the development of methods of measurement for semiconductor materials, process control, and devices. The emphasis is on silicon device technologies. Principal accomplishments during this reporting period include (1) identification of surface preparation procedures which improve the quality of spreading resistance measurements, (2) preparation of a videotaped tutorial discussion of thermally stimulated current and capacitance measurements, (3) completion of an analysis of the apparent position of an opaque edge when viewed with incoherent and coherent illumination, and (4) completion of the construction of a flying-spot scanner. Results are also reported on capacitance-voltage and two-probe resistivity measurements; analyses of thermally stimulated current and capacitance measurements on metaloxide-semiconductor (MOS) capacitors; a review of methods for characterizing interface states associated with thin oxide films on silicon; fabrication of a test pattern based on the charge-coupled device; a preliminary comparison of filar and image shearing eyepieces for line-width measurement; a review of technologies in use for photomask inspection and measurements; procedures for determination of correct photoresist exposure; epitaxial layer thickness; scanning electron microscopy; mathematical modeling of ultrasonic bonding; leak test procedures; thermal resistance measurements on transistors and Darlington pairs; and transistor thermal response measurements. Supplementary data concerning staff, publications, workshops and symposia, standards committee activities, and technical services are also included as appendices.

Key Words: Boron redistribution; Darlington pairs; dopant profiles; electrical properties; electronics; epitaxial

layer thickness; flying-spot scanner; gold-doped silicon;

hermeticity; measurement methods; microelectronics; micrometrology; MOS devices; oxide films; photomasks; photoresist;

resistivity; scanning electron microscopy; semiconductor

devices; semiconductor materials; semiconductor process control; silicon; spreading resistance; test patterns; thermal

resistance; thermal response; thermally stimulated capacitance; thermally stimulated current; ultrasonic bonding; voltage contrast mode; wire bonds.

# 1. INTRODUCTION

This is a report to the sponsors of the Semiconductor Technology Program on work during the twenty-fourth quarter of the Program. It summarizes work on a wide variety of measurement methods for semiconductor materials, process control, and devices that are being studied at the National Bureau

of Standards. The Program, which emphasizes silicon-based device technologies, is a continuing one, and the results and conclusions reported here are subject to modification and refinement.

The work of the Program is divided into a number of tasks, each directed toward the study of a particular material or device property or measurement technique. This report is subdivided according to these tasks. Highlights of activity during the quarter are given in section 2. Subsequent sections deal with each specific task area. References cited are listed in the final section of the report.

The report of each task includes a narrative description of progress made during this reporting period. Additional information concerning the material reported may be obtained directly from individual staff members identified with the task in the report. The organization of the Program staff and telephone numbers are listed in Appendix A.

Background material on the Program and individual tasks may be found in earlier quarterly reports as listed in Appendix B. From time to time, publications are prepared that describe some aspect of the program in greater detail. Current publications of this type are also listed in Appendix B. Reprints or copies of such publications are usually available on request to the author.

Communication with the electronics community is a critical aspect both as input for guidance in planning future program activities and in disseminating the results of the work to potential users. Formal channels for such communication occur in the form of workshops and symposia sponsored or co-sponsored by NBS. Currently scheduled seminars and workshops are listed in Appendix C. In addition, the availability of proceedings from past workshops and seminars is indicated in the appendix.

An important part of the work that frequently goes beyond the task structure is participation in the activities of various technical standardizing committees. The list of personnel involved with this work given in Appendix D suggests the extent of this participation. In most cases, details of standardization efforts are reported in connection with the work of a particular task.

Technical services in areas of competence are provided to other NBS activities and other government agencies as they are requested. Usually these are short-term, specialized services that cannot be obtained through normal commercial channels. To indicate the kinds of technology available to the Program, such services provided during the period covered by this report are listed in Appendix E.

# 2. HIGHLIGHTS

Particularly significant accomplishments during this reporting period include (1) identification of surface preparation procedures which improve the quality of spreading resistance measurements, (2) preparation of a videotaped tutorial discussion of thermally stimulated current and capacitance measurements, (3) completion of an analysis of the apparent position of an opaque edge when viewed with incoherent and coherent illumination, and (4) completion of the construction of a flying-spot scanner.

In addition, a Symposium on Spreading Resistance was held in June at NBS, Gaithersburg under the joint sponsorship of NBS and ASTM Committee F-l on Electronics. At the symposium, 90 participants representing 53 organizations from seven countries heard 24 papers which demonstrated that the spreading resistance technique, first utilized in the semiconductor industry more than 10 years ago, is beginning to receive wide acceptance as a measurement tool and is now appreciated as a method offering both high spatial resolution and great flexibility in terms of the variety and complexity of semiconductor structures to which it can be applied. The proceedings of the symposium are being published separately. See Appendix C for a summary of this and other dissemination activities.

Highlights of progress in technical task areas are listed below.

Resistivity; Dopant Profiles — A significant advance was made in the understanding of the influence of surface preparation techniques on spreading resistance measurements, and several improved procedures for preparing polished surfaces suitable for making spreading resistance measurements were identified. It appears to be possible to trace a variety of previously encountered problems to the aqueous nature of the polishing medium. To obtain stable surfaces, water residues must be thoroughly removed or non-aqueous polishing media employed.

Junction capacitance-voltage measurements were made on a series of diodes of four different sizes formed by diffusion into a uniformly doped wafer. These measurements were made in an experiment to test the various correction factors applied in the algorithm for reducing capacitance voltage data. Since these factors depend strongly on the area-to-periphery ratio, it is important to establish their validity over a range of diode sizes of interest. Satisfactory results were achieved.

Further progress was made in the analysis of the boron redistribution problem and the results of an interlaboratory evaluation of the two-probe method for measuring resistivity of silicon crystals, conducted in cooperation with ASTM Committee F-1, were analyzed and reported.

Initial attempts were made to profile the middle layer of a three layer structure, equivalent to profiling the base of a transistor, by means of the junction capacitance-voltage method. Difficulties not accounted for by the models being used to analyze the data were encountered and are being further investigated. Work on the reevaluation of Irvin's curves

which relate resistivity to impurity density was directed this quarter primarily toward development of the fixture suitable for automated differential sheet resistance measurements.

<u>Crystal Defects and Contaminants</u> — The physical model which had been developed to predict the dynathermal current and capacitance response of the gold acceptor center in silicon was improved by incorporating a more complete expression for the depletion width in an MOS capacitor. This improvement will facilitate the extension of the model to other impurities and defect centers.

As an experiment in new forms of dissemination of information, a 35-minute tutorial videotape, Defects in p-n Junctions and MOS Capacitors Observed using Thermally Stimulated Current and Capacitance Measurements, was produced late in the quarter. This full color videotape is available for distribution on loan without charge. As an added feature, arrangements can be made for the author to be available for a telephone conference call to answer questions and provide more detailed information, following a prearranged showing of the videotape.

Oxide Film Characterization — Three electrical techniques for measuring interface state densities were analyzed and compared. Preliminary measurements were made to test sodium contamination levels of various processing materials. A detailed review of the sensitivities, sampling volumes, and other characteristics of various surface analysis techniques was undertaken. Study of ion microprobe mass analysis and x-ray photoelectron spectroscopy continued along previously reported lines.

<u>Test Patterns</u> — Design work for the charge coupled device test structures, being conducted at the Naval Electronics Laboratory Center, has been completed and the mask set prepared. In addition analysis of the charge coupled device in several operating modes has been initiated to establish the algorithms necessary to extract the desired parameter information from the experimental measurements.

<u>Photolithography</u> — Visits to an additional 15 device manufacturers, photomask and photoresist suppliers, and manufacturers of mask alignment or inspection equipment confirmed the four major problem areas previously identified: line width measurement, edge definition, mask and photoplate inspection, and mask registration. Initial efforts in the next phase of this work include a study to quantify the effects responsible for obtaining different dimensional measurements on the same artifact when using a filar or image shearing eyepiece and a thorough analysis of the various technologies now being used or proposed for use to automatically inspect photomasks for defects, pattern errors, or registration faults. This work is being conducted in cooperation with the Lawrence Livermore Laboratory. The photomask industry has particularly emphasized the importance of development by NBS of standards for line width measurements at the 1 μm level.

An analysis of the apparent position of an opaque edge of ideal geometry when viewed through a microdensitometer showed that the true edge was at the half power point for incoherent illumination and at the quarter power point for coherent illumination.

<u>Epitaxial Layer Thickness</u> — Preliminary comparisons were made between the step-relaxation method, one of two thickness measurement methods based on use of the transient high-frequency capacitance-voltage characteristic of an MOS capacitor, and the infrared reflection and spreading resistance methods.

<u>Wafer Inspection and Test</u> — Work was completed on the assembly of the flying-spot scanner intended to evaluate electrical properties of devices before and after exposure to the electron beam of the scanning electron microscope. In addition, a cylindrical detector intended to increase the sensitivity of the scanning electron microscope in the voltage contrast mode was assembled and installed.

<u>Interconnection Bonding</u> — The effort on mathematical modeling of the motion of an ultrasonic wire bonding tool, undertaken to determine the mechanisms by which the metallurgical weld is formed and to lay the basis for a quantitative in-process monitoring scheme, resulted in an analysis which qualitatively predicts the normalized vibration amplitude of a variety of bonding tools of different sizes and materials.

Hermeticity — Interlaboratory evaluation of the helium mass spectrometer and radioisotope techniques for measurement of fine leaks are being conducted in cooperation with ASTM Committee F-1. Preliminary evaluation of the novel procedure for a dry, quantitative gross leak test began. A sensitive mass spectrometer was constructed for use in evaluating this type of instrumentation for the measurement of trace elements in the semiconductor processing environment and on wafer surfaces as well as for the investigation of gas flow mechanisms in leaks in hermetic packages.

<u>Thermal Properties of Devices</u> — An analysis showed that the overlap diode model can be used to explain several experimental observations of differences between apparent thermal resistance as measured with the emitter-base and collector-base junction voltages as temperature sensitive parameters on wide-base and narrow-base transistors. Preliminary measurements of thermal resistance were made on commercial Darlington circuits.

A one dimensional model for power transistor cooling was shown to predict transient thermal response for periods up to 250  $\mu s$ . With the model, it is possible to estimate both average junction temperature and area of power generation at steady state from experimental measurements of the cooling curve.

Impact of Automation on Measurement Requirements — Initial efforts have begun on a study of automated integrated circuit processing and assembly contracted to Arthur D. Little. This work is intended to provide additional criteria for selection of priorities to be assigned in connection with measurement method development in the program. Initial results suggest that considerable attention should be directed toward routinely used wafer measurements: sheet resistance; thickness of oxide, epitaxial or diffused layers; visual inspection; and capacitance-voltage.

# 3. RESISTIVITY; DOPANT PROFILES

#### 3.1. Spreading Resistance Methods

Surface preparation procedures which improve the quality of spreading resistance measurement have been identified [1]. Erratic behavior and poor reproducibility had been observed, especially on p-type specimens with resistivity greater than 1  $\Omega$ ·cm, when constructing calibration curves for use with the spreading resistance instrument (NBS Tech. Note 806, pp. 9-10). Later in measuring radial resistivity profiles of the 10  $\Omega$ ·cm p-type wafers intended for use as one of the set comprising Standard Reference Material 1520 (NBS Tech. Note 806, p. 66), it was found that the spreading resistance method gave much greater variability (on a macroscopic scale) than either the four-probe method suitably corrected for off-center measurement [2] or the photovoltaic method [3]. During the present quarter, unexpectedly large level shifts in spreading resistance were observed on beveled 10  $\Omega$ ·cm p-type specimens between the freshly polished bevel surface and the unpolished original top surface.

In all cases, the surfaces had been chem-mechanically polished with an aqueous based silica sol [4]. A series of experiments was carried out on beveled specimens similar to those on which the level shifts had been observed. After polishing, the specimens were bathed or swabbed in a solution of hydrofluoric acid, chromic acid, ammonium hydroxide, or ammonium hydroxide and hydrogen peroxide but in no case was there reasonable agreement between the spreading resistance value on the beveled surface and that on the original top surface. Baking out the specimen at 70 to 100°C under partial vacuum for 15 min also failed to resolve the discrepancy. Comparison of these observations with those of members of other laboratories led to the recommendation that the bakeout temperature be at least 150°C.

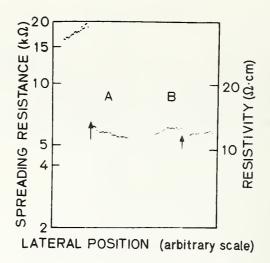

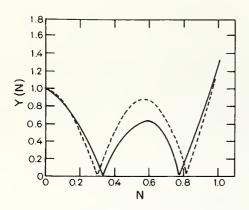

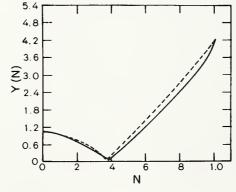

This higher temperature bakeout treatment in partial vacuum was applied for 15 min to specimens that had been bevel polished with silica aquasol and other polishing materials with the results that the spreading resistance value did not change significantly from one side of the bevel vertex to the other and it also corresponds with the resistivity as measured by the four-probe method [5]. An example of these results is shown in figure 1. In related experiments it was also observed that polishing media which are not aqueous based do not require the high temperature bakeout; this observation is in good agreement with those of Mayer and Schwartzmann [6].

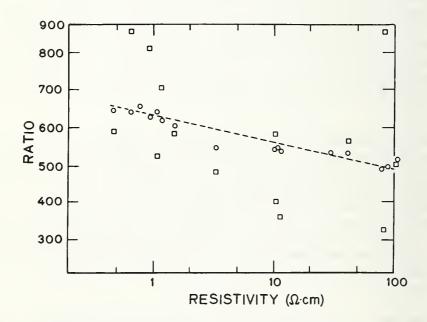

After the wafers were baked at 150°C for 15 min the scatter around the calibration curve regression line was considerably reduced. This is illustrated in figure 2 where the ratio of spreading resistance to resistivity as measured by the four-probe method is plotted against the resistivity.

<sup>\*</sup> A. Mayer, RCA, Somerville, New Jersey 08876 (private communication).

Figure 1. Spreading resistance of a 10  $\Omega \cdot \text{cm}$  p-type silicon specimen bevel polished with silica aquasol. (A: Not baked out; B: Baked out after polishing. In each case, the arrow indicates the position of the bevel vertex.)

Figure 2. Ratio of spreading resistance to four-probe resistivity for p-type silicon wafers polished with silica aquasol. ( $\mathbf{0}$ : Not baked out;  $\mathbf{0}$ : Baked out after polishing.)

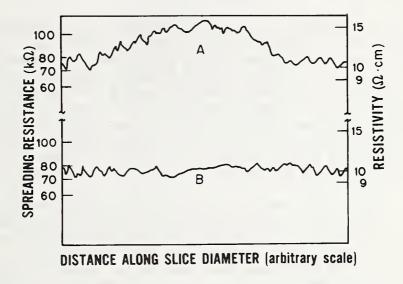

Figure 3. Radial resistivity profile of a 10  $\Omega \cdot \text{cm } p$ -type silicon wafer polished with silica aquasol. (A: Not baked out; B: Baked out after polishing.)

It should be noted that this mode of presentation enhances departures from the line of regression which might be lost in the conventional log-log plot of spreading resistance against resistivity.

A 15 min bakeout at 160°C also improved the quality of macroscopic radial resistivity profiles determined by the spreading resistance method as illustrated in figure 3. For this wafer the profile as measured by either four-probe and photovoltaic techniques showed variation of less than ±5 percent. The upper plot in the figure which was taken along a diameter after polishing but before bakeout shows an apparent variation of about 50 percent, but after the bakeout the variation is reduced to that of the other methods as shown in the lower plot.

Although the mechanism for the observed surface effects is not fully understood, it is probably associated with the aqueous nature of the polishing media. Such effects may be reduced by variation of polishing conditions such as loading, rate of surface feed, or the nature of the polishing substrate, but bakeout after polishing has been shown to remove the effects almost completely. It must be noted that the magnitude of the effects may be related to conductivity type or resistivity level or both. Hence, isolated experiments on a limited number of specimens may be inadequate to characterize a particular polishing process for the full spectrum of specimen types which may eventually be encountered. (J. R. Ehrstein)

#### 3.2. Junction Capacitance-Voltage Method

An experiment was carried out to obtain a preliminary assessment of the adequacy of available peripheral [7,8] corrections for use in deducing dopant density from capacitance-voltage measurements on gated  $p^+n$  junction diodes of different sizes. The experiment involved analysis of capacitance-voltage data taken on the four gated p-n junction diode test structures on test pattern NBS-2 (NBS Tech. Note 788, pp. 15-17) [10]. Three of these structures (Nos. 1, 6, and 9) are circular, with diameters of 6, 20, and 60 mils (0.15, 0.5, and 1.5 mm), respectively; the fourth (No. 4) is square, 18 mils (0.44 mm) on a side. The pattern is repeated every 200 mils (5.08 mm) in both directions over the wafer.

Measurements were made on wafer 575, an initially homogeneous 10  $\Omega \cdot \text{cm}$ , n-type wafer, which was selected after preliminary measurements indicated that the dopant density was relatively independent of depth and that the flat-band voltage was fairly constant over the wafer surface. Measurement was attempted on each gated p-n junction of the four types on the slice. Reverse bias voltages of 2, 5, 10, and 20 V were applied. At each voltage the capacitance was measured with the gate biased at -6.7 V which represented a nominal value of flat-band voltage for the wafer. The dimensions of three to five diodes of each type were measured on photomicrographs and an average diameter or width was calculated for each type. An area was calculated from this average diameter or width for use in all dopant density calculations for each type of diode.

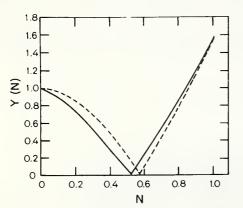

Because of gate-to-substrate shorts, gate-to-diffused layer shorts, or excessive leakage, not all devices could be measured. Three values of dopant density were computed for each measurable diode by using differences in capacitance measured at 2 and 5 V, 5 and 10 V, and 10 and 20 V. The peripheral correction for the circular junctions was performed using eq (3) of [7] assuming  $W_2 = W_{\rm t}$  and  $W_1 = 0$  as defined therein. The peripheral correction for the square junction was performed using eq (16) of [8] making similar assumptions. Diffused layer corrections [9] were also applied. The average and the percent relative sample standard deviation of the three dopant density values were calculated for each measurable diode, and a map of the average values was made as shown in figure 4. The groups of four in the figure represent the four diodes within a cell

On the map of figure 4 there are twelve squares in which all four diodes were measurable. These 48 diodes constituted a statistical population which was subjected to analysis to determine whether on the average all diode geometries gave the same dopant density values. The grand average dopant density, N, calculated for each diode type, is listed in table 1. All four values of N fall within a range less than 3 percent of the

of the test pattern. The dashes denote diodes which could not be measured. Values in parentheses indicate that a measurement was made but that it was rejected because of excessive deviation from the average or

excessive scatter.

|                          | 3.96<br>3.89<br>4.09           | 4.05<br>4.03<br>3.92<br>4.07   | 4.07<br>4.15<br>3.98<br>4.15 | 3.91<br>4.09             | 3.92<br>3.92<br>4.15         |                              |

|--------------------------|--------------------------------|--------------------------------|------------------------------|--------------------------|------------------------------|------------------------------|

| 4.02<br><br>3.99         | (4.36)<br>4.01<br>3.95         | 4.18<br>4.07<br>4.00<br>4.02   | 4.17<br>4.03<br>4.03<br>4.03 | 4.11<br><br>3.97<br>4.17 | 3.97<br>3.94<br>4.11         | 3.88<br>4.21                 |

| 4.08<br>4.00<br><br>4.09 | 4.26<br>4.14<br>(4.56)<br>4.06 | 4.18<br><br>4.04<br>4.04       | 4.18                         | 4.00<br>(10.0)           | 4.06<br>4.03<br>4.11         | 4.07<br>3.96<br>3.94<br>4.14 |

| (4.53)<br>3.86           | 4.17<br>4.17<br>4.18<br>4.12   | 4.20<br>4.07<br>4.04<br>4.24   | 4.16<br>4.08<br><br>4.17     | 4.11<br><br>4.01<br>4.02 | 4.11<br>4.03<br>4.04<br>4.09 | 4.08<br>3.96<br>3.94<br>4.11 |

| 3.89<br>4.11             | 4.28<br>4.10<br>4.09<br>4.22   | 4.14                           | 4.11<br>4.07<br>4.04<br>4.14 | 4.11<br>4.07<br>4.18     | 4.13<br><br>4.02             | 4.07<br>3.92                 |

|                          | 4.11<br><br>3.88<br>4.04       | (6.32)<br>4.00<br>3.94<br>4.05 | 4.11<br>4.04<br>4.12         | 4.04<br><br>4.09         | 4.01<br>3.93<br>3.94<br>4.11 |                              |

|                          |                                | (4.06)<br>3.86                 | 3.91                         | <br>4.04                 |                              |                              |

Figure 4. Wafer map of average dopant density derived from capacitance-voltage measurements. (Each group of four numbers represents measurements made within a unit cell of test pattern NBS-2 on slice 575. Dopant densities as measured on structures 4, 9, 6, and 1 are listed from top to bottom in each group. The boxed data were used in the statistical analysis described in the text. The data of figure 5 were taken on the cell marked with an asterisk.)

Table 1 — Oopant Oensity Profiles from Capacitance-Voltage Measurements

| Diode<br>Type | N, cm <sup>-3</sup>     | s <sub>N</sub> , 9 | N <sub>1</sub> , cm <sup>-3</sup> | N <sub>3</sub> , cm <sup>-3</sup> | Δ, % |

|---------------|-------------------------|--------------------|-----------------------------------|-----------------------------------|------|

| 4             | 4.13 × 10 <sup>14</sup> | 0.82               | 4.10 × 10 <sup>1</sup>            | 4.16 × 10 <sup>1</sup>            | 1.46 |

| 9             | 4.05                    | 1.20               | 4.01                              | 4.10                              | 2.30 |

| 6             | 4.01                    | 1.14               | 3.97                              | 4.06                              | 2.22 |

| 1             | 4.12                    | 0.64               | 4.11                              | 4.13                              | 0.54 |

| A11           | 4.08                    | 0.95               | 4.05                              | 4.11                              | 1.63 |

overall grand average for all 48 diodes listed in the bottom line of the table. For the same population, the percent relative sample standard deviations for each type were averaged to obtain the values  $\mathbf{S}_{\mathrm{N}}$  listed in

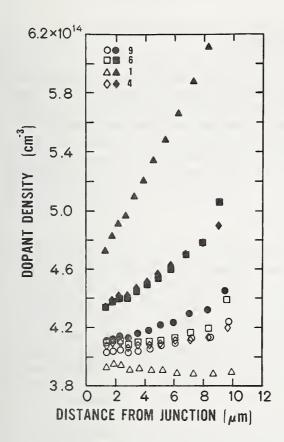

table 1. Most of the variability was due to the fact that there was a systematic increase in calculated dopant density as the reverse bias was increased. To examine this systematic increase the dopant densities computed from measurements at 2 and 5 V and at 10 and 20 V were averaged for each diode type to obtain  $N_1$  and  $N_3$ , respectively. These values are listed in table 1 together with  $\Delta$ , the percent increase of  $N_3$  over  $N_1$ . Except for the case of the 6-mil diodes,  $S_N$  is only 50 to 60 percent of

$\Delta.$  For the 6-mil diodes,  $S_{\rm N}$  is greater than  $\Delta$  which suggests that in this case  $S_{\rm N}$  is dominated by random error (such as that introduced by stray capacitance) rather than the systematic increase. This is not unexpected since stray capacitance is a more significant error source for the smaller diodes.

To demonstrate the need for the peripheral correction, the capacitances of the four diodes in the cell indicated by an asterisk in figure 4 were measured for reverse biases of 0, 0.5, 1, 2, 3, 5, 7, 10, 14, 20, 27 and 35 V and the dopant density was calculated for each adjacent pair of capacitance values with and without the peripheral correction applied. The results are shown in figure 5. For this experiment the measuring system was modified such that the meters for reading the capacitance and bias voltage were powered through line voltage regulators to suppress noise and the digital voltmeter for reading the output of the capacitance meter was operated in a filtered mode to achieve resolution to four significant figures. In addition the calculations were made with values of area calculated from the measured dimensions of each diode in the cell rather than from the averaged dimensions used in the previously described analysis. The diffused layer correction was applied throughout. The particularly good agreement of the corrected profiles of the 18-, 20- and 60-mil diodes is evident. The corrected profile of the 6-mil diode is about 5 percent below the other three. This discrepancy might arise because the peripheral capacitance comprises a comparatively large percentage of the measured capacitance in the case of the 6-mil diodes as indicated in table 2. The fact that a one-sided junction is assumed in calculating the peripheral capacitance leads to a systematic error which is greatest when the peripheral capacitance is a significant fraction of the measured capacitance. There is also a discrepancy between the dopant densities of figures 4 and 5 for the particular diodes in question. This discrepancy is due in part to the fact that different areas were used to obtain the values of dopant density presented in the two figures and in part to differences in the experimental set ups. The relative importance of these two causes may be assessed by examining table 3 in which are shown the dopant densities as determined using both measuring systems and both sets of area values. As expected, the differences in area result in identical shifts for both measuring systems. The variation between measuring systems

Figure 5. Apparent dopant density determined from capacitance-voltage measurements with (open data points) and without (solid data points) application of the peripheral correction. (The diffused layer correction was applied in both cases. Measurements were made on the cell marked with an asterisk in figure 4.)

Table 2 — Ratio of Peripheral Capacitance to Measured Capacitance

| Diode Type | C <sub>p</sub> /C <sub>m</sub> , % |

|------------|------------------------------------|

| 4          | 5.98                               |

| 9          | 1.88                               |

| 6          | 5.43                               |

| 1          | 16.28                              |

|            |                                    |

Table 3 — Dopant Density from Capacitance-Voltage Measurements Taken and Analyzed in Different Ways

|               | Measuring Sys                            | stem #1 (fig. 4)                         | Measuring System #2 (fig. 5)          |                                          |  |

|---------------|------------------------------------------|------------------------------------------|---------------------------------------|------------------------------------------|--|

| Diode<br>Type | Average Dimension                        | Individually-Measured<br>Dimension       | Average Dimension                     | Individually-Measured<br>Dimension       |  |

| 4             | 4.16 × 10 <sup>14</sup> cm <sup>-3</sup> | 4.18 × 10 <sup>14</sup> cm <sup>-3</sup> | $4.07 \times 10^{14} \text{ cm}^{-3}$ | 4.09 × 10 <sup>14</sup> cm <sup>-3</sup> |  |

| 9             | 4.00                                     | 4.04                                     | 4.03                                  | 4.07                                     |  |

| 6             | 4.00                                     | 4.17                                     | 3.94                                  | 4.11                                     |  |

| 1             | 4.05                                     | 4.01                                     | 3.95                                  | 3.91                                     |  |

appears to be random and may be due as much to other sources of random error as to changes in the measuring system.

Considering the experimental conditions and uncertainties which have been discussed, it may be tentatively concluded that dopant densities can be calculated from junction C-V data which are precise to within a few percent independent of geometry for diodes having geometries similar to those which have been studied. Confirmation of this conclusion requires collection and analysis of a larger amount of data.

(R. L. Mattis and M. G. Buehler)

#### 3.3. Mathematical Models of Dopant Profiles

Starting with appropriate initial concentrations  $C_1(z, 0)$  and  $C_2(y, 0)$  at time t = 0, and appropriate boundary conditions, the Volterra integral equations discussed previously (NBS Spec. Publ. 400-4, pp. 9-11) were solved for the two unknown heat potentials  $Q(\tau)$  and  $R(\tau)$  in the infinitesimal dimensionless time interval  $\Delta t = \tau_2 - \tau_1$  where  $\tau_1 = 0$ . Next, from the definitions of  $C_1(z, t)$  and  $C_2(y, t)$  in terms of  $Q(\tau)$  and  $R(\tau)$ , the values of  $C_1(z, \Delta t)$  and  $C_2(y, \Delta t)$  in their appropriate domains were calculated. By using these quantities as new initial distributions and repeating the previous cycle of computations the values of  $C_1(z, t)$  and  $C_2(y, t)$  were calculated at times 2  $\Delta t$ , 3  $\Delta t$ , . . . These values of the concentrations were then compared with the known exact solutions of Grove, Leistiko and Sah [11]. The comparison showed good agreement in the interior of each domain but the values of C1 and C2 at the moving boundary drifted uniformly upward instead of remaining constant as they should have. The instability seemed to be inherently connected with the fact that  $C_1(y, t)$  and  $C_2(z, t)$  were being computed and used in each cycle of the computations. A modified program has been written in which only the initial values of  $C_1(y, t)$  and  $C_2(z, t)$  are used to compute  $Q(\tau)$ and  $R(\tau)$  for all times  $\Delta t$ , 2  $\Delta t$ , . . . The new program, written in (S. R. Kraft\* and M. G. Buehler) FORTRAN, is being debugged.

#### 3.4. Two-Probe Method

The results of an interlaboratory round-robin evaluation of a two-probe method for measuring resistivity of cylindrical ingots were analyzed. The round robin had been conducted by ASTM Committee F-l on Electronics which developed the test method [12]. Eight cylindrical silicon crystals with room temperature resistivity in the range 9  $\times$  10 $^{-4}$  to 4  $\times$  10 $^3$   $\Omega \cdot$ cm were used in the round robin. Each participating laboratory was asked to make five independent measurements for each of two orientations 90 deg apart around the circumference at each of 11 lengthwise positions on each

<sup>\*</sup> Mathematical Analysis Section, Applied Mathematics Division, NBS.

crystal. Five laboratories participated. One reported data as required, the second reported five measurements per position which not only did not seem to be independent but also exhibited apparent transcription errors, the third reported only an apparent average value at each position on only five of the crystals, the fourth produced some data useful for comparison but these data were not complete enough to be used in the analysis, and the fifth produced no usable data. It is not certain that the positions were numbered from the same end by each laboratory. It is assumed that the orientations were held constant for each crystal by any one participant, but that they differed from laboratory to laboratory for the same crystal. In most cases, the number of significant figures reported varied from laboratory to laboratory.

Since the method of test centers on the average of five measurements for any one position, it would have been preferable to analyse the round robin in terms of such averages. However, because of the way in which data were reported from the several laboratories, it was judged that analysis in terms of the median of a set of five readings would be more reliable. For sample size five, from normal distribution, the variability of medians is only slightly larger than that of means, and median values are much less sensitive to outliers. Of course, for the laboratory reporting only averages, the average value had to be substituted for the median.

In the following discussion, the crystals are numbered 1 to 8 in order of increasing resistivity. Analysis was based on data from crystals as follows: from crystals 1, 2, and 3: two labs, eleven positions, and two orientations; from crystals 4, 5, 6, 7, and 8: three labs, eleven positions, and two orientations. This data base, though meager, was adequate to estimate the variability of the method.

One way analyses of variance were done for each crystal, to check for significant differences between laboratory-orientation combinations. There were eleven measurements (positions) for each class (laboratory-orientation). Statistically significant differences were observed in half the crystals; these were investigated further in subsequent analyses.

Separate two way analyses for laboratory and lengthwise position effects were run for each crystal, with both orientations being averaged at each position. A significant lengthwise position effect was observed on all crystals except crystals 5 and 8, and a moderately significant laboratory effect was observed on all crystals except crystals 5 and 7. Residuals from these two way analyses normalized to the means cover a range of one order of magnitude in a reasonably random fashion, whereas the absolute resistivity values of specimens spanned 6 1/2 orders. This suggests that the random variability increases with resistivity and that variability expressed as a percentage of the mean might be expected to be reasonably constant.

Table 4 — Analysis of Two-Probe Resistivity Round Robin

|         | Grand Average | rand Average Difference of Lab Average of L<br>lesistivity, from Grand Average, % percen |       | Range<br>of Lab                   | Estimate<br>of              | Difference from Grand Average, % |                                   |       |

|---------|---------------|------------------------------------------------------------------------------------------|-------|-----------------------------------|-----------------------------|----------------------------------|-----------------------------------|-------|

| Crystal | Resistivity,  |                                                                                          |       | Averages,<br>percentage<br>points | Standard<br>Deviation,<br>% | of Lowest<br>Position<br>Average | of Highest<br>Position<br>Average |       |

| 1       | 0.000929      | -0.23                                                                                    | +0.23 |                                   | 0.46                        | 1.9                              | - 3.4                             | + 6.2 |

| 2       | 0.0163        | +0.15                                                                                    | -0.15 |                                   | 0.30                        | 1.2                              | - 2.5                             | + 3.6 |

| 3       | 0.128         | -0.20                                                                                    | +0.20 |                                   | 0.40                        | 1.6                              | - 3.8                             | + 2.8 |

| 4       | 1.55          | -0.07                                                                                    | -0.60 | +0.67                             | 1.27                        | 3.6                              | - 1.4                             | + 1.4 |

| 5       | 11.7          | -0.57                                                                                    | ~0.65 | +1.22                             | 1.87                        | 5.3                              | - 1.9                             | + 4.5 |

| 6       | 155.          | +0.40                                                                                    | -0.65 | +0.25                             | 1.05                        | 2.9                              | - 2.0                             | + 1.0 |

| 7       | 1007.         | -0.20                                                                                    | +0.70 | -0.50                             | 1.20                        | 3.3                              | <b>-</b> 12.                      | +31.  |

| 8       | 3190.         | +3.0                                                                                     | +3.9  | -6.9                              | 10.8                        | 30.                              | - 3.2                             | + 5.1 |

Regressions were done against position, for each laboratory and each crystal, to see if the position differences were consistent over laboratories. Residuals from low-order polynomial fits were remarkably similar across laboratories, indicating that there were definite position effects. The specific order of polynomal is not important; the significant result is that the resistivity is a smooth function of lengthwise position and its variation is large compared to inherent measurement variability. That is, the lengthwise variations are real, not artifacts of data scatter masked by a paucity of laboratories.

For each crystal, the average of all measurements made by each laboratory was computed. A grand average of these laboratory averages was also calculated for each crystal. These are listed in column 2 of table 4. The percent deviations of the laboratory averages from the grand average are listed in columns 3 to 5 of the table. The range of these deviations, listed in column 6 of the table, was used for estimating the overall measurement variability of this method. The values for range can be converted into estimates of standard deviation by multiplying by the factors 0.86 and 0.59 for two-laboratory and three-laboratory data, respectively. Since the range values are based on averages of 22 individual medians (two orientations, eleven positions) it is necessary to multiply by an additional factor of  $\sqrt{22}$  to obtain an estimate of the standard deviation for the individual medians of five measurements. These estimates are listed in column 7 of the table.

Crystal 8 required further investigation. Laboratory 3 showed significant negative bias for this crystal, position by position, as well as in average value. The average bias for laboratory 3 on this crystal with

respect to the average of the other two laboratories is -10.3 percent. Considering only the measurements by laboratories 1 and 2, the estimate of standard deviation of medians of five repetitions is reduced to less than 3 percent. However, if the data of laboratory 3 are retained but translated to remove the bias, and if the variability of the bias of each of the three laboratories is considered, the standard deviation is estimated to be approximately 10 percent.

On the basis of the data available, it seems reasonable to conclude that a laboratory similar to the participants in the experiment, working carefully, and taking the mean or median of five repetitions at one location on a crystal, will estimate the true resistivity with a standard deviation of 4 percent or less when the resistivity is 1000  $\Omega$  cm or less, and with a standard deviation of about 10 percent for a resistivity in the neighborhood of 3500  $\Omega$  cm.

Taking the calculations one step farther, one sees that the 3-sigma limits for the "true" value of resistivity at a given point are at  $\pm 12$  percent from the mean of a set of five repetitions at that point, for resistivities up to 1000  $\Omega$  cm, and at  $\pm 30$  percent for resistivities near 3500  $\Omega$  cm.

In addition, an estimate was made of the lengthwise variation of resistivity for each crystal. This was done by first taking the average of medians for both orientations and all laboratories at each lengthwise position of each crystal. The lowest and highest such averages are indicative of the lengthwise resistivity variation. These averages, expressed as percent differences from the grand average for the crystal, are listed in columns 8 and 9, respectively, of table 4.

Finally, an estimate was made of variability within one laboratory. For the set of data which was most complete, the ranges of the sets of five repetitions were calculated for each orientation and each position, for each ingot. These ranges were then averaged for each ingot, and converted to estimates of the standard deviation of a median or mean of five repetitions. The values obtained ranged from 0.04 percent to 0.5 percent, for crystals 1 to 7 and 1.3 percent for crystal 8. Eliminating the two positions on each end of crystal 8 reduced its value to 0.8 percent. Now 0.5 percent is markedly less than the several percent obtained when analyzing results from several laboratories. This is not surprising; in fact, it would be surprising if measurements taken by one laboratory did not cluster better than those taken by several different laboratories. It is, however, another justification for the word of caution about unexplained sources of variation that ought to accompany all precision statements, especially those involving only one laboratory or one experimenter or one technique. (J. R. Ehrstein and J. A. Lechner\*)

<sup>&</sup>quot;Statistical Engineering Section, Applied Mathematics Division, NBS.

# 4. CRYSTAL DEFECTS AND CONTAMINANTS

#### 4.1. Thermally Stimulated Current and Capacitance Measurements

The theoretical model for the dynathermal current and capacitance responses of an MOS capacitor reported previously (NBS Tech. Note 806, pp. 13-16, NBS Spec. Publ. 400-1, pp. 16-19, and NBS Spec. Publ. 400-4, pp. 27-33) has been solved numerically and the dynathermal current response plotted as a function of temperature. The numerical solution involves solving the transcendental expression for the depletion width W of an MOS capacitor. This can be computed by integration of the previously reported derivative equation [eq (11) of NBS Spec. Publ. 400-4, p. 31] with the constant of integration evaluated at time zero where W equals its initial phase I value. The resultant equation for an n-MOS capacitor is:

$$\left(\frac{\varepsilon_{s}^{X_{o}}}{\varepsilon_{o}} + W_{IIf}\right) \ln \left(\frac{W - W_{IIf}}{W_{Ii} - W_{IIf}}\right) = W_{Ii} - W + \left(\frac{\varepsilon_{s}^{X_{o}}}{\varepsilon_{o}} + \frac{W_{IIf}}{2}\right) \ln \left(\frac{N_{d} - N_{t}}{N_{d} - n_{t}}\right) - \frac{\varepsilon_{s}^{X_{o}}}{\varepsilon_{o}} \int_{0}^{t} \frac{p_{t}^{e_{p}} dt}{(N_{d} - n_{t})} + \frac{1}{2} \int_{0}^{t} \frac{W \frac{dn_{t}}{dt}}{(N_{d} - n_{t})} dt \tag{1}$$

where  $W_{\rm Ii}$  is the depletion width at the beginning of phase I,  $W_{\rm IIf}$  is the depletion width after phase II,  $\varepsilon_{\rm o}$  is the dielectric constant of silicon dioxide,  $\varepsilon_{\rm s}$  is the dielectric constant of silicon,  $X_{\rm o}$  is the oxide thickness,  $p_{\rm t}$  is the hole density at a defect center,  $e_{\rm p}$  is the hole emission rate,  $n_{\rm t}$  is the electron density at a defect center,  $N_{\rm t}$  is the acceptor defect dopant density, and  $N_{\rm d}$  is the donor dopant density. Temperature dependent terms are W,  $e_{\rm p}$ ,  $p_{\rm t}$ , and  $n_{\rm t}$ .

Values for  $W_{1i}$  and  $W_{1lf}$  are obtained from measured values of capacitance:

$$W_{T_i} = \varepsilon_S A(C_{T_i}^{-1} - C_{O}^{-1})$$

and

$$W_{\text{IIf}} = \varepsilon_s A(C_{\text{IIf}}^{-1} - C_0^{-1})$$

where A is the area of the MOS capacitor and  $C_{\rm Ii}$ ,  $C_{\rm IIf}$ , and  $C_{\rm o}$  are the capacitances measured at the beginning of phase I, at the end of phase II, and with the capacitor forward biased into accumulation as shown in the

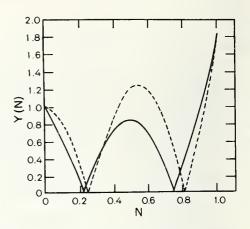

idealized curves in figure 6. Equation (1) was solved iteratively at various temperatures. At the lowest temperature the initial value of W was taken as  $W_{1i}$ . This was inserted into the right-hand side of eq (1) and a new value for W was obtained. The process was repeated by substituting the previous value of W in the right-hand side of eq (1) and solving for a new value until successive values of W differed by less than  $10^{-3}$  W. The process was then repeated for higher temperatures by using as the initial value of W the value found at the next lower temperature.

Plots of depletion width against temperature for the gold acceptor in an n-MOS silicon capacitor are shown in figure 7 for temperatures from 180 to 320 K. The heating rate  $\beta$  was taken as 10 K/s,  $C_{\text{o}}$  as 14.00 pF,  $C_{\text{IIf}}$  as 7.33 pF, and  $C_{\text{Ii}}$  as 3.20 pF. For curves A and B, the ratio  $N_{\text{d}}/N_{\text{t}}$  was taken as 25 while for curve C it was taken as 5. Curves B and C were computed from the complete equation. For curve A it was assumed that  $(dn_{\text{t}}/dt)$  = 0; in this case terms 3 and 5 on the right-hand side of eq (1) become zero.

Dynathermal current response of gold acceptors in an n-MOS capacitor was calculated from the previously reported equation [eq (12) of NBS Spec. Publ. 400-4, p. 31] for current. The quantity W was calculated from eq (1),  $e_n$  and  $e_n$  were calculated from previously reported expressions [eqs (6) and (7) of NBS Spec. Publ. 400-4, pp. 27, 29] and  $n_t$  and  $p_t$  were calculated from integral equations reported elsewhere [13]. Since eqs (7c) and (7d) of [13] greatly exceed the capability of calculators with only 12 significant figures, it was necessary to reformulate them in such a way that the magnitudes could be reduced by approximately the tenth root and that the values could be accumulated incrementally in order to avoid fatal round-off errors. Geometrical parameters were chosen to correspond with those of Device No. 2107.7 on which experimental dynathermal response has been reported (NBS Spec. Publ. 400-1, p. 17). Plots were made of current as a function of temperature for heating rates of 0.5, 1, 2, 5, and 10 K/s. The general shape of the curves agrees very well with the experimental curves obtained on Device No. 2107.7. Comparisons of the theoretical and experimental phase I and phase II emission temperatures have been given previously (NBS Spec. Publ. 400-4, pp. 32-33) as plots of heating rate against emission temperature. The peaks of the theoretical current response are in excellent agreement with the theoretical plot of heating rate against phase II emission temperature. (W. E. Phillips and M. G. Buehler)

Figure 6. Capacitance-voltage characteristic and dynathermal current and capacitance response of an ideal, gold-doped n-MOS capacitor.

Figure 7. Calculated depletion width of a gold-doped silicon n-MOS capacitor during dynathermal response measurements. (See text for a discussion of conditions for each curve.)

Figure 8. Calculated phase I and phase II dynathermal current response to gold acceptors in a silicon n-MOS capacitor for various heating rates.

# 5. OXIDE FILM CHARACTERIZATION

#### 5.1. Measurement of Interface State Density

Electronically active defects located near the interface of a siliconsilicon dioxide structure give rise to various effects, such as carrier trapping and injection, which can degrade device performance. These interface states are known as fast states: because they can readily exchange charge with the bulk silicon. These states can be characterized by their charge, their capture cross section, and their density and distribution in energy across the band gap of silicon.

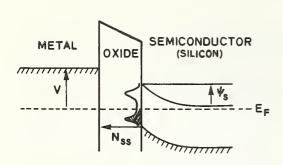

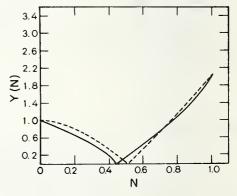

Three techniques for measuring the interface state density and energy distribution were reviewed. Each of these techniques involves the measurement of characteristics of MOS capacitors: the low frequency capacitance-voltage (C-V) characteristic, the temperature dependence of the high frefrequency C-V characteristic, or the frequency and bias dependence of the conductance.

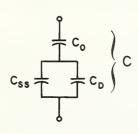

Use of the low frequency C-V characteristic to determine interface state densities was first suggested by Berglund [14]. The basic assumption is that the a-c test frequency is low enough that all interface states remain in thermal equilibrium. Consider the band diagram and equivalent circuit for the MOS capacitor in figure 9. The oxide capacitance, semiconductor depletion capacitance, and the surface state capacitance, all per unit area, are shown as  $C_0$ ,  $C_D$ , and  $C_{ss}$ , respectively; C is the total measured capacitance per unit area. There are no loss elements since it is assumed that the surface states and the semiconductor space charge are in equilibrium. The d-c bias, V, applied to the MOS capacitor results in a surface potential,  $\psi_s$ ; the Fermi energy,  $E_{\rm p}$ , is constant throughout the structure. The interface state density,  $N_{ss}$ , is shown schematically on the band diagram. For any given surface potential only the interface states near the Fermi energy communicate with the bulk silicon. Therefore, by sweeping the Fermi energy across the gap (by varying the applied potential which, in turn, varies the surface potential) it is possible to

From the equivalent circuit, it is evident that:

$$C_{ss} = \left(\frac{C}{1 - \frac{C}{C_o}} - C_D\right).$$

determine the distribution of interface states in the forbidden gap.

The term, fast state, is a relative notion since a state which is fast at room temperature (i.e., which can readily exchange charge with the bulk) may not be fast at low temperature.

#### a. Energy band diagram.

#### b. Equivalent circuit.

Figure 9. Representations of an MOS capacitor in the low frequency approximation. (See text for discussion of symbols.)

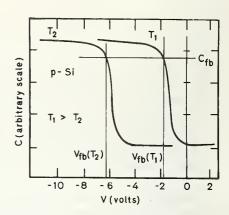

a. High frequency capacitance-voltage curves which show shift in flat-band voltage.

b. Silicon energy band diagram which shows shift in Fermi energy.

Figure 10. Effect of temperature on properties of a p-MOS capacitor. (See text for discussion of symbols.)

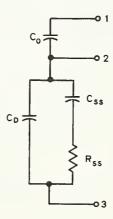

Figure 11. Equivalent circuit used for the analysis of the conductance technique. (See text for discussion of symbols.)

Since C is determined by biasing the capacitor into accumulation, the first term in the brackets is explicitly determined from the experimental C-V characteristic. Given the dopant density, and the area and oxide thickness of the capacitor,  $C_D(\psi_s)$  can be calculated [15]. Note that  $C_D$  is a function of  $\psi_s$  while C is a function of V. Therefore, it is also necessary to develop a relationship between  $\psi_s$  and V. Berglund [14] showed that:

$$\psi_{s}(V_{1}) - \psi_{s}(V_{2}) = \int_{V_{1}}^{V_{2}} \left(1 - \frac{C(V)}{C_{o}}\right) dV.$$

(2)

Except for the constant of integration, the potential can be calculated simply from the experimental data. The integration constant is determined by comparing the potential curve calculated from eq (2) with the potential curve calculated from ideal C-V characteristics [15]. It is thus possible to relate the interface state density to the low frequency capacitance,  $C(\psi_{\text{c}}(\text{V}))$ :

$$N_{ss}(\psi_s) = \frac{C_{ss}(\psi_s)}{q} = \frac{1}{q} \left( \frac{C(\psi_s(V))}{C(\psi_s(V))} - C_D(\psi_s) \right).$$

For a particular value of  $\psi_s$ , the position of the Fermi energy above the valence band edge at the surface is given by  $\Delta = E_F - E_{V(bulk)} - \psi_s$  (for n-type material) or by  $\Delta = \psi_s + E_F - E_{V(bulk)}$  (for p-type material).

Traditionally, the low frequency C-V characteristic has been measured using lock-in techniques. However, for frequencies below 5 Hz, this method becomes difficult. An alternative is to use the quasi-static technique [16]. In this method, the displacement current of the MOS capacitor is measured in response to a slow linear voltage ramp. If the ramp is "slow enough" (5 to 500 mV/s), the surface states remain in equilibrium and the displacement current is proportional to the low frequency capacitance.

The second technique to be considered is the temperature dependence of the high frequency C-V characteristic. This is the Gray-Brown [17] method where the flat band voltage of the MOS capacitor is monitored as the temperature is varied. An example of a high frequency C-V characteristic and a simplified silicon band diagram are shown in figure 10 for the case of a p-MOS capacitor. At temperature  $T_1$ , the Fermi level is assumed to be above the surface states which are filled and electrically neutral. As the temperature is lowered, the Fermi level moves closer to the valence

band edge; this causes depopulation of the surface states. The loss of electrons at the interface requires a larger negative bias voltage in order to maintain the flat band condition. Thus, as the temperature is lowered the C-V characteristic (for p-type devices) shifts to the left. The experimental procedure is to record the flat band voltage,  $V_{fb}(T)$ , as a function of temperature by monitoring the flat band capacitance,  $C_{fb}$ .

The change in the flat band voltage is directly related to a change in the charge at the interface. Similarly the change in the surface potential with temperature is directly related to the shift in the Fermi energy. A graphical differentiation of a plot of the charge as a function of surface potential yields the interface state density. This technique is effective only around a small region of the band gap near the majority carrier band edge. Probing of the surface states near both the valence and conduction band requires both p-type and n-type specimens.

The third technique for measuring interface state density is the conductance method of Nicollian and Goetzberger [18]. In this technique, the frequency and bias dependence of MOS conductance is measured. Nicollian and Goetzberger showed that the conductive losses in the semiconductor space charge region and the oxide are negligible; hence, the a-c conductance in an MOS structure is due entirely to the interface states.

The simplified equivalent circuit for the MOS capacitor with surface states is shown in figure 11. The capacitive elements were defined in the discussion of figure 9b; the loss element associated with the interface states is  $R_{\text{ss}}$ . Experimentally, the appropriate measurement is to determine the impedance of the MOS capacitor,  $Z_{13}$ , as a function of frequency for values of bias from depletion to inversion. From each value of  $Z_{13}(\omega,V)$ , the oxide reactance,  $Z_{12} = 1/j\omega C_0$ , is subtracted and the result inverted to obtain the admittance, Y23, associated with the semiconductor portion of the structure. For each value of bias voltage (V( $\psi_{_{\rm S}}$ )), the maximum in the real part of the admittance determines C  $_{_{\rm SS}}$ and  $N_{SS}(\psi_S)$ . It is only necessary to find the relation between V and  $\psi_S$ . This can be done by the Berglund procedure [14] which was discussed earlier. Although this technique allows the probing of regions away from the band edges, it does not give information near the middle of the gap. To get data in both halves of the gap requires the use of both n-type and p-type specimens.

Of the three methods considered here, it is generally acknowledged that the conductance technique gives the most accurate results. However, it requires the collection of much data on both types of specimens and fails to obtain information in the mid-gap region. The temperature technique does not require as much data as the conductance technique but also suffers from lack of information in the mid-gap region. However, it does very well near the band edges, but requires both types of specimens. The

quasi-static technique is able to probe the entire mid-gap region using either type of specimen and fails to probe only the band edge region. It also has the advantage of being a relatively simple experiment to conduct.

(R. Y. Koyama)

#### 5.2. Sodium Contamination Studies

To test the sodium contamination levels of various materials routinely used in the processing facility, analyses were made with a flame spectrometer. Most materials studied exhibited sodium levels of 0.5 parts per million or less. The photoresist developer contained about 1.7 percent sodium. The results of these analyses are summarized in table 5. The technique is sensitive to less than 0.1 parts per billion sodium and has an estimated accuracy of ±25 percent or better, at this level.

Samples of oxidized silicon treated with photoresist and developer are currently being prepared to study the amount of sodium which is transferred from the developer to the oxide during processing.

(T. C. Rains: and S. Mayo)

Table 5 -- Flame Spectrometer Analysis for Sodium Contamination

| Material                          | Sodium Level, ng/ml    |  |  |

|-----------------------------------|------------------------|--|--|

| Photoresist                       | 50                     |  |  |

| Photoresist Developer             | 16.8 × 10 <sup>6</sup> |  |  |

| Hydrogen Peroxide                 | 250                    |  |  |

| Ammonia                           | 8                      |  |  |

| Buffered Etch for Silicon Dioxide | 100                    |  |  |

| Hydrochloric Acid                 | 500                    |  |  |

| Acetone                           | 0.8                    |  |  |

<sup>&</sup>quot;NBS Spectrochemical Analysis Section, Analytical Chemistry Division.

# 6. TEST PATTERNS

#### 6.1. Charge-Coupled Device Test Pattern