### National Institute of Standards and Technology

Technology Administration

U.S. Department of Commerce

NISTIR 6933

January 2003

ELECTRONICS AND ELECTRICAL ENGINEERING LABORATORY

# SEMICONDUCTOR Electronics Division

**P**ROGRAMS, **A**CTIVITIES, AND **A**CCOMPLISHMENTS

# THE ELECTRONICS AND ELECTRICAL ENGINEERING LABORATORY (EEEL)

One of NIST's seven measurement and standards laboratories, EEEL conducts research, provides measurement services, and helps set standards in support of the fundamental electronic technologies of semiconductors, magnetics, and superconductors; information and communications technologies, such as fiber optics, photonics, microwaves, electronic displays, electronics manufacturing supply chain collaboration; forensics and security measurement instrumentation; fundamental and practical physical standards and measurement services for electrical quantities; maintaining the quality and integrity of electrical power systems; and the development of nanoscale and microelectromechanical devices. EEEL provides support to law enforcement, corrections, and criminal justice agencies, including homeland security.

EEEL consists of six programmatic divisions and two matrixmanaged offices:

**Electricity Division**

Semiconductor Electronics Division

Radio-Frequency Technology Division

Electromagnetic Technology Division

**Optoelectronics Division**

Magnetic Technology Division

Office of Microelectronic Programs

Office of Law Enforcement Standards

This publication describes the technical programs of the Semiconductor Electronics Division. Similar documents describing the other Divisions and Offices are available. Contact NIST/EEEL, 100 Bureau Drive, MS 8100, Gaithersburg, MD 20899-8100, telephone 301-975-2220, http://www.eeel.nist.gov. These publications are updated biennially.

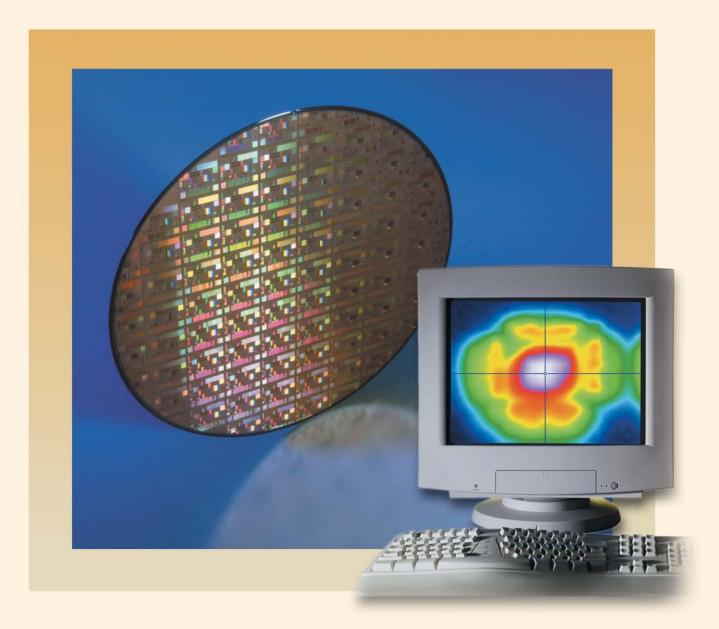

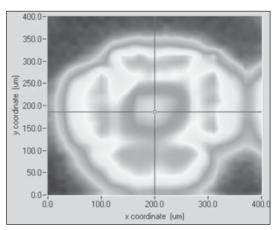

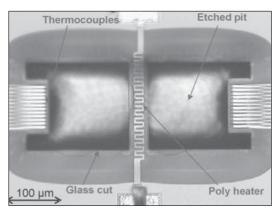

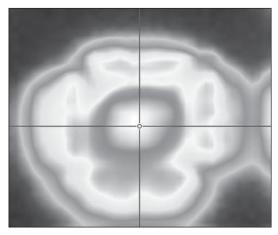

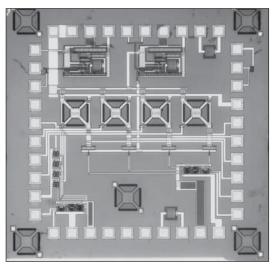

*Cover caption: (front to back) a thermal image of a MEMS-based hotplate during a transient event and an IBM 200 mm EDRAM Wafer (photo by Tom Way, courtesy of International Business Machines Corporation. Unauthorized use not permitted.).*

ELECTRONICS AND ELECTRICAL ENGINEERING LABORATORY

# SEMICONDUCTOR Electronics Division

# **P**ROGRAMS, **A**CTIVITIES, AND **A**CCOMPLISHMENTS

NISTIR 6933

January 2003

U.S. DEPARTMENT OF COMMERCE Donald L. Evans, Secretary

Technology Administration Phillip J. Bond, Under Secretary of Commerce for Technology

National Institute of Standards and Technology Arden L. Bement, Jr., Director

Any mention of commercial products is for information only; it does not imply recommendation or endorsement by the National Institute of Standards and Technology nor does it imply that the products mentioned are necessarily the best available for the purpose.

# CONTENTS

| Welcome                                                                                                              | iv    |

|----------------------------------------------------------------------------------------------------------------------|-------|

| Mission                                                                                                              | vi    |

| Vision                                                                                                               | vi    |

| Values                                                                                                               | vi    |

| Goals                                                                                                                | vi    |

| Semiconductors: Backbone of the Electronic/Digital Revolution                                                        | . vii |

| Semiconductor Electronics Division Organization                                                                      | ix    |

| Scanning-Probe Microscope Metrology                                                                                  | 1     |

| Advanced MOS Device Reliability and Characterization                                                                 | 5     |

| Nanoelectronic Device Metrology                                                                                      | 9     |

| Thin-Film Process Metrology                                                                                          | . 13  |

| Power Semiconductor Device and Thermal Metrology                                                                     | . 18  |

| MicroElectroMechanical Systems                                                                                       | . 22  |

| Electrical Test Structure Metrology                                                                                  | . 25  |

| Major Facilities / Laboratories                                                                                      | . 30  |

| Microfabrication Process Facility                                                                                    | . 31  |

| National Research Council (NRC) Post-Doctoral Opportunities                                                          | . 34  |

| 2003 International Conference on Characterization and Metrology for ULSI Technology,<br>Mar. 24–28, 2003, Austin, TX | . 38  |

| Gaitan Receives DoC Silver Medal Award                                                                               |       |

| Division Teamwork Team Receives DoC Bronze Medal Award                                                               | . 40  |

| Integrated Circuit Gas Sensing System Technology Valuable for Homeland Security                                      | . 41  |

| SPS Intern Contributes to Division Research                                                                          | . 42  |

| Transfer of Equipment to the University of Puerto Rico at Mayaguez Strengthens Power Electronics Research            | . 43  |

| Educational Outreach by Division Staff                                                                               |       |

| Future NIST Cleanroom Facility on Track for Spring 2003 Completion                                                   |       |

| NIST's Gaithersburg, Maryland Campus and Surrounding Area                                                            |       |

|                                                                                                                      |       |

David G. Seiler, Division Chief

"The Semiconductor **Electronics Division has** played a key role in the phenomenal growth of the semiconductor industry and in helping U.S. companies maintain leadership in the development and manufacture of silicon and compound semiconductors. NIST continues to provide the state-of-the-art measurement capabilities and standards necessary to support industry's ongoing efforts to push physical and chemical limits in the production of new devices and processes."

> NRC Panel Report, An Assessment of the National Institute of Standards and Technology Measurement and Standards Laboratories: Fiscal Year 2001

# WELCOME

The Semiconductor Electronics Division (SED) provides leadership in developing the semiconductor measurement infrastructure essential to improving U.S. economic competitiveness. It provides necessary measurements, physical standards, and supporting data and technology; associated generic technology; and fundamental research results to industry, government, and academia. The primary mission of the Division is to provide the measurement infrastructure to U.S. industry for mainstream silicon CMOS (complementary metal-oxide semiconductor) technology. The Division's programs also respond to industry measurement needs related to MicroElectroMechanical Systems (MEMS), power electronics, and compound semiconductors.

The Division has extensive interactions with individual companies, industry organizations, and professional societies; these activities enable the development of a research agenda responsive to the needs of industry. Active participation in industry roadmapping, such as the Semiconductor Industry Association's International Technology Roadmap for Semiconductors, and standards activities, such as committee work for the American Society for Testing and Materials, is practiced by the Division to prioritize and establish programs with the highest potential impact. The Division widely disseminates the results of its research, especially in the areas of standardized test methods and Standard Reference Materials (SRMs), through a variety of channels: publications, software, conferences and workshops, and participation in standards organizations and consortia. NIST also actively seeks industrial, academic, and non-profit research partners to work collaboratively on projects of mutual benefit.

The Division, with a staff of about 70 including full-time and part-time employees as well as guest researchers, is based in Gaithersburg, Maryland. The Division is one of six divisions within the Electronics and Electrical Engineering Laboratory at NIST. The Division's technical activities are organized into four groups: the Materials Technology Group, the Advanced Microelectronics Technology Group, the Device Technology Group, and the IC Technology Group. The Division assists industry by providing tools such as SRMs, test chips, standard reference data, and software that support the needed measurement infrastructure. Division personnel visit industrial sites, host a variety of visitors, and make available tutorial material on an as-needed basis. We also are active in conference and workshop activities that directly benefit the industry. The Division receives and is responsive to hundreds of special requests for assistance from industry each year.

A broad array of activities that serve the semiconductor industry is currently underway in the Division. The staff of the SED addresses projects ranging from materials qualification to test structures for integrated circuits. Some of these projects are supported by the NIST National Semiconductor Metrology Program (NSMP), which is managed by the Electronics and Electrical Engineering Laboratory's Office of Microelectronic Programs. For more information on the NSMP, go to www.eeel.nist.gov/omp.

The Division, in cooperation with the National Research Council (NRC), offers awards for post-doctoral research for U.S. citizens in a variety of fields related to the semiconductor electronics industry. For additional details, including field descriptions and qualification guidelines, please see page 34.

The technical programs, activities, and accomplishments described here for each Division project clearly demonstrate the impact of the SED's leadership and effective service as it continues to respond to the needs of industry and to contribute to the scientific and engineering communities.

Please take an opportunity to visit our Division Web site at www.eeel.nist.gov/812/. In addition to providing further details on our Division and up-to-date project information, our Web site has interactive tutorials on the Hall effect (www.eeel.nist.gov/812/hall.html) and MEMS standard test structures based on e-standards (www.eeel.nist.gov/812/test-structures/).

Thank you for your interest in our Division! I welcome your comments and suggestions. Feel free to e-mail me at david.seiler@nist.gov.

David H. Seiler

David G. Seiler Division Chief

Semiconductor Electronics Division Staff

For additional information, contact:

Division/Office Telephone: 301-975-2054 Division/Office Facsimile: 301-975-6021 On the Web: www.eeel.nist.gov/812/ "The nature of the vision's purpose is not only to achieve a meaningful strategic or company goal, but also to build a dedicated community"

> Jay A. Conger, The Brave New World of Leadership Training, IEEE Eng. Mgmt. Review (1996)

The Division mission, vision, values, and goals were developed by a strategic planning process facilitated by a professional consultant. This process involved extensive workforce involvement, the Division leadership, and numerous meetings and informal discussions.

# MISSION

The **Semiconductor Electronics Division** provides leadership in developing the semiconductor measurement infrastructure essential to improving U.S. economic competitiveness by providing necessary measurements, physical standards, and supporting data and technology; associated generic technology; and fundamental research results to industry, government, and academia. The primary focus is on mainstream silicon CMOS (complementary metal-oxide semiconductor) technology. The Division's programs also respond to industry measurement needs related to MicroElectroMechanical systems (MEMS), power electronics, and compound semiconductors.

# Vision

The **Semiconductor Electronics Division** is recognized as a dynamic world-class resource for semiconductor measurements, data, models, and standards focused on enhancing U.S. technological competitiveness in the world market.

# VALUES

The **Semiconductor Electronics Division** values its commitment to identify and to meet crucial measurement technology needs. The Division values its collaboration with all segments of the semiconductor community. It strives for integrity, excellence, objectivity, responsiveness, and creativity, while maximizing and utilizing the potential of its employees.

# GOALS

The Division will:

- Aggressively pursue and achieve select metrology needs as identified in the International Technology Roadmap for Semiconductors for mainstream silicon.

- Develop new and improved process-monitoring tools, methodologies, and data for the more efficient manufacture of silicon and compound-semiconductor devices.

- Develop cooperative, multidisciplinary projects within the Division and synergistic external collaborative efforts to better meet the critical needs of the semiconductor industry.

- Support novel research that has high potential for providing breakthroughs in materials, process, devices, and measurement technologies for the semiconductor industry.

# SEMICONDUCTORS: BACKBONE OF THE ELECTRONIC/DIGITAL REVOLUTION

"This year the semiconductor industry will manufacture about 60 million transistors for every man, woman and child on earth. By 2008, chipmakers will be producing 1 billion transistors or more per year. Transistors improve our lives in countless ways—they make cars safer and more fuel-efficient, they enable personal communication devices, they promote medical breakthroughs and they improve the quality of education."

- Building Blocks for Innovation, Semiconductor Industry Association (SIA) Annual Report 2002, p. 17

For the past 20 years, the personal computer reigned supreme as the driver of semiconductor industry growth. But new leadership is emerging. The communications revolution, perhaps the defining social and economic transition of our time, is fueled by the ever smaller, ever cheaper, ever faster invention of the chip industry. The explosive demands of the wireless, broadband Internet and optical networking industries have crowned the communications chip as the dominant end market for semiconductors.

- Information technology (IT) continues to be the primary driver of the U.S. economy, and U.S. semiconductor companies are leading the charge. American chipmakers now supply nearly half of the world's chips.

- U.S. chipmakers add more value to the national economy than any other industry.

- For 50 years, the semiconductor industry has provided the bricks and mortar that built the modern world. The exciting expansion in semiconductor applications means our job has only just begun and that our industry's greatest growth lies ahead.

- Personal communications devices will become so functional as to be indispensable, cars will be safer and more fuel-efficient, the quality of education will improve, chips implanted in our bodies will tell our doctor we're sick before we register symptoms. Eventually silicon and biology will converge, and the biocomputer will seem no more novel than today's laptop. As *Forbes ASAP* Editor Michael Malone has noted, "the microprocessor is the defining invention of the electronic age, the inventor of inventions."

- adapted from the Semiconductor Industry Association (SIA) 2001 Annual Report, pp. 2-5.

Semiconductors, transistors, and their applications represent one of the greatest scientific and technological breakthroughs of the twentieth century. Consider their far reaching influence on our society in general and our daily lives. Can you imagine life without them? Semiconductors are pervasive in the microelectronic components used in computers, entertainment equipment, automotive electronics, medical instrumentation, telecommunications, space technology, television, radio, cell phones, and many other information technologies. Every hospital, school, factory, car, airplane, office, bank, and household contains transistors, microprocessors, and other semiconductor devices.

These breakthroughs are possible because of the miniaturization of the transistor dimensions, which allows the construction of compact systems with tremendous computing power and memory. Miniaturization, in turn, is possible because of the perfection of fabrication techniques that allow the "integration" of circuits and thus the production of chips containing millions of elements per square centimeter. The foundation stone of this complex technology is silicon. Meeting the demands for these large-scale, complex, integrated circuits (ICs) continues to require technological advances in materials, processing, circuit design, characterization, testing, and standards.

"No other human invention is the equal of the semiconductor device - if only because no other invention has been adopted so quickly and pervasively as the integrated circuit. Since the invention of the planar process forty years ago, billions of transistors are now in use beneath, around and above the earth. The microprocessor is the defining invention of the electronic age, the inventor of inventions from the personal computer to the internet."

> The Silicon Century, Semiconductor Industry Association (SIA) Annual Report and Directory 2000

"Private sector and government collaboration is essential to our continued progress. For example, the National Institute of Standards and Technology is developing standards for measuring the evershrinking line widths that characterize semiconductor products. Industry alone cannot develop these new standardsgovernment must oversee the process."

> Building Blocks for Innovation, Semiconductor Industry Association (SIA) Annual Report 2002, p. 20.

The semiconductor electronics industry is outstripping the measurement capability needed for maintaining and improving U.S. international competitiveness. Important factors affected include product performance, price, quality, compatibility, and time to market. The Division provides the measurement capability needed to support the efforts of U.S. industry to improve its competitiveness. In order to support this effort, the Division also engages in technology development and fundamental research, and makes the findings available to industry.

The Division focuses the largest part of its resources on the development and delivery of measurement capability for two principal reasons: measurement capability has a very high impact on U.S. industry because it helps manufacturers address many of the challenges they face in realizing competitive products in the marketplace, and NIST is the official lead U.S. Government agency for measurements.

The Division focuses on developing measurement capability that is beyond the reach of the broad range of individual companies. Companies seek NIST's help for several reasons:

- The companies need NIST's special technical capability for measurement development.

- The companies need NIST's acknowledged impartiality for diagnosing a measurement problem affecting the industry broadly or for achieving adoption of a solution across the industry.

- The companies cannot develop the measurement capability needed by the industry broadly because they cannot individually capture the returns of the cost of development.

- Industry's quality standards require that key measurements be traceable to the national measurement reference standards that NIST maintains. This is a requirement of growing importance in export markets.

The Division continues to interact and collaborate with a wide variety of companies, consortia [such as International Semiconductor Manufacturing Technology (ISMT), Semiconductor Equipment and Materials International (SEMI), and the Semiconductor Research Corporation (SRC)], academia, and other government labs to accomplish its mission. Specific details are given in the project sheets that follow. Work in the Division results in extensive outputs or deliverables that cover knowledge and improvements in physical understanding, test methods and measurements, Standard Reference Materials (SRMs), Standard Reference Data (SRD) sets, standards, test structures and test chips, software, measurement accuracy and traceability, publications and reports, patents and Cooperative Research and Development Agreements (CRADAs), round robins, data and models, talks and short courses, company visits, conferences and workshops, consortia participation, and various activities and leadership roles on committees and working groups.

Division staff serve the semiconductor community in leadership roles on standards committees such as American Society for Testing and Materials (ASTM) and Electronic Industries Alliance (EIA) / Joint Electron Device Engineering Council (JEDEC), societies such as IEEE, ECS, and APS, and on numerous semiconductor conferences/workshops. Many test methods and standards have been developed and written over the years by NIST staff for ASTM and EIA/JEDEC, including ones for resistivity, oxygen in silicon, thin dielectrics, electromigration, and device characterization. Staff serve on various Technical Working Groups to help put together the International Technology Roadmap for Semiconductors (ITRS). These groups are Process Integration, Devices, and Structures; Assembly and Packaging; Lithography; Interconnect; and Front End Processes. The ITRS provides targets for equipment, material, and software suppliers; provides targets for researchers; and serves as a common reference for the semiconductor industry.

The Division also has impacted the semiconductor community by producing a number of SRMs. To date, over 2,500 SRMs have been sold and distributed for resistivity, oxygen in silicon, and optical thickness by ellipsometry. Hundreds of companies throughout the world have purchased these SRMs to maintain and improve their measurement capability.

# SEMICONDUCTOR ELECTRONICS DIVISION

# ORGANIZATION

# **DIVISION OFFICE (812.00)**

| 2054 | SEILER, David G., Chief       | 5633 | MURPHY, Joan, Admin. Assistant (PT) |

|------|-------------------------------|------|-------------------------------------|

| 2068 | BLACKBURN, David L., Deputy   | 2079 | BENNETT, Herbert S., NIST Fellow    |

| 2054 | GUARIGLIA, Lori A., Secretary | 2097 | HARMAN, George G., NIST Fellow      |

| 4514 | COOK, Sharon W., AO           | 2050 | SECULA, Erik M.                     |

|      |                               |      |                                     |

# MATERIALS TECHNOLOGY GROUP (812.01)

8009 SHAFFNER, Thomas J. (GL) 2053 HUFF, Barbara, Secretary

#### SCANNING-PROBE MICROSCOPE METROLOGY

| 2089 | KOPANSKI, Joseph J. (PL) |

|------|--------------------------|

| 2075 | ALBERS, John             |

| 3241 | BIRDWELL, A. Glen (PD)   |

| 8755 | BUH, Gyoung-Ho (GR)      |

| 2088 | MARCHIANDO, Jay F.       |

| 2067 | THURBER, W. Robert       |

| 8009 | SHAFFNER, Thomas J.      |

## THEORETICAL SOLID-STATE PHYSICS FOR **SEMICONDUCTORS (FA)**

2079 BENNETT, Herbert S. (FL)

#### **ADVANCED MICROELECTRONICS TECHNOLOGY GROUP (812.02)**

| 4723 | VOGEL, Eric M. (GL)        |

|------|----------------------------|

| 2053 | HUFF, Barbara, Secretary   |

| 2052 | WILKES, Jane M., Secretary |

### **ADVANCED MOS DEVICE RELIABILITY** AND CHARACTERIZATION

| 2247                            | SUEHLE, John S. (PL) |

|---------------------------------|----------------------|

| 2053                            | BAYNE, Anthony (GR)  |

| 2078                            | EDELSTEIN, Monica D. |

| 5373                            | HAN, Jin-Ping (GR)   |

| 5466                            | HEAD, Linda (GR)     |

| 8687                            | HEH, Da-Wei (GR)     |

| 5145                            | KIM, Jin Yong        |

| 4723                            | VOGEL, Eric M.       |

| 2111                            | ZHU, Baozhong        |

| NANOELECTRONIC DEVICE METROLOGY |                      |

#### 2082 RICHTER, Curt A. (PL) EDELSTEIN, Monica D. 2078 2053 GNADE, Bruce (GR) 2233 HACKER, Christina (PD) 5373 HAN, Jin-Ping (GR)

| ; | MURPHY, Joan, Admin. Assistant (PT) |

|---|-------------------------------------|

| ) | BENNETT, Herbert S., NIST Fellow    |

| 7 | HARMAN, George G., NIST Fellow      |

| ) | SECULA, Erik M.                     |

| 2087 | KIRILLOV, Oleg     |

|------|--------------------|

| 2053 | PARK, Jin-Won (GR) |

| 2247 | SUEHLE, John S.    |

| 4723 | VOGEL, Eric M.     |

#### **THIN-FILM PROCESS METROLOGY**

| 2060 | EHRSTEIN, James R. (PL)  |

|------|--------------------------|

| 5974 | AMIRTHARAJ, Paul M. (GR) |

| 2084 | CHANDLER-HOROWITZ, Deane |

| 8747 | CHO, Yong J. (GR)        |

| 2044 | NGUYEN, Nhan V.          |

| 2082 | RICHTER, Curt A.         |

| 2065 | RICKS, Donnie R.         |

|      |                          |

## **DEVICE TECHNOLOGY GROUP (812.03)**

- 2071 HEFNER, Allen R., Jr. (GL)

- 2056 KROFT, Terri S., Secretary

#### **POWER DEVICE AND THERMAL METROLOGY**

| 2071 | BLACKBURN, David L. (PL) |

|------|--------------------------|

| 2069 | BERNING, David W.        |

| 2242 | BUCK, Laurence M.        |

| 2071 | HEFNER, Allen R., Jr.    |

| 4709 | JOSHI, Yogendra K. (GR)  |

| 2056 | LAI, Jih-Sheng (GR)      |

| 2056 | MANTOOTH, Homer (GR)     |

| 8776 | McNUTT, Ty R. (GR)       |

| 2056 | NOAMAN, Bassam           |

| 5967 | REICHL, John V. (GR)     |

| 8751 | TIGLI, Onur (GR)         |

|      |                          |

#### MICROELECTROMECHANICAL SYSTEMS

| 2070 | GAITAN, Michael (PL)         |

|------|------------------------------|

| 2056 | ETINA, Natalya (S)           |

| 5484 | GEIST, Jon (GR)              |

| 4739 | HERMAN, David L. (GR)        |

| 4710 | JAHN, Andreas (GR)           |

| 2049 | MARSHALL, Janet C. (PT)      |

| 6367 | MIJARES, Geraldine I.        |

| 2045 | MORGAN, Nicole (PD)          |

| 6347 | POLK, Brian (PD)             |

| 5466 | REYES-HERNANDEZ, Darwin (PD) |

| 4710 | SWOPE, Bretton M. (S)        |

| 2056 | WEI, Xiaojin (GR)            |

|      |                              |

#### Legend:

AO = Administrative Officer FA = Focus Area FH = Faculty Hire FL = Focus Area Leader FM = Facility Manager GL = Group Leader GR = Guest Researcher PD = Post-Doctoral Appointment PL = Project Leader PT = Part TimeS = Student

Telephone numbers are: (301) 975-XXXX (the four digit extension as indicated)

#### METROLOGY FOR SYSTEMS-ON-A-CHIP (FA)

- 8777 MICHELET, Robert W. (FL)

- 5420 AFRIDI, Muhammad Y. (GR)

- 2069 BERNING, David W.

- 2236 ELLENWOOD, Colleen E.

- 2071 HEFNER, Allen R., Jr.

- 8751 TIGLI, Onur (GR)

- 2239 ZAGHLOUL, Mona E. (FH)

#### Wire Bonding to Cu/Low- $\kappa$ Semiconductor Devices (FA)

2097 HARMAN, George G. (FL)

## IC TECHNOLOGY GROUP (812.04)

- 2052 LINHOLM, Loren W. (GL)

- 2052 WILKES, Jane M., Secretary

#### ELECTRICAL TEST STRUCTURE METROLOGY

- 2072 CRESSWELL, Michael W. (PL)

- 5026 ALLEN, Richard A.

- 4446 GHOSHTAGORE, Rho (GR)

- 8193 MURABITO, Christine E. (S)

- 5623 OWEN, James C.

- 2234 SCHAFFT, Harry A. (GR)

- 2182 YARIMBIYIK, Emre

#### **MICROFABRICATION PROCESS FACILITY**

- 2699 HAJDAJ, Russell (FM)

- 2096 JOHNSON, Eric S.

#### Legend:

- AO = Administrative Officer

- FA = Focus Area

- FH = Faculty Hire

- FL = Focus Area Leader

- FM = Facility Manager

- GL = Group Leader

- GR = Guest Researcher

- PD = Post-Doctoral

- Appointment

- PL = Project Leader

- PT = Part Time

- S = Student

Telephone numbers are: (301) 975-XXXX (the four digit extension as indicated)

# SCANNING-PROBE MICROSCOPE METROLOGY

### GOALS

Develop advanced scanning-probe and conventional electrical metrology techniques, models, and artifacts that are essential to improving semiconductor materials, processes, device performance, and reliability for the silicon and compound semiconductor industries. A current specific goal is to provide the technology computer-aided design (TCAD) community with quantitative twodimensional dopant profiles to calibrate and enhance the predictivity of simulators.

Gyoung-Ho Buh (left) and Glen Birdwell (right) loading a sample onto the stage of the modulation/ surface photovoltage spectroscopy system.

## **CUSTOMER NEEDS**

The Semiconductor Industry Association's (SIA's) International Technology Roadmap for Semiconductors (ITRS) identifies 2-D and 3-D carrier profiling as a key enabling technology for the development of next-generation integrated circuits. In 2003, it is desired to know 2-D carrier profiles with spatial resolution of 5 nm and with a precision (in concentration) of  $\pm 5$  %; these demands increase to less than 1 nm and  $\pm 2$  % by 2015. The Scanning Capacitance Microscope (SCM) has emerged as the leading contender to provide 2-D carrier profiles.

While SCMs are commercially available, techniques to interpret SCM images accurately have lagged. Much work remains to be done to develop 3-D physical models of scanning capacitance microscopy and techniques to use these models to extract quantitative carrier profiles from SCM images of differential capacitance. Likewise, the measurement methodology for quantitative scanning capacitance microscopy is still evolving. The need for, and form of, reference materials for scanning capacitance microscopy has yet to be defined. Other scanning probe microscopy (SPM) based techniques for semiconductor metrology suffer similar problems; microscopes have been invented, but standard measurement and interpretation techniques are not available.

## **TECHNICAL STRATEGY**

The Scanning-Probe Microscope Metrology Project is developing tools that are intended to enable scanning capacitance microscopes to function as two-dimensional dopant profiling tools. This work is divided into three tasks. Task 1 is development of SCM measurement methodologies. Best measurement practices are being determined via collaborative projects with industrial users and research into the physics of the silicon surface preparation. Task 2 is development of theoretical models of the SCM. The focus of our modeling effort has been to develop 2-D and 3-D finiteelement solutions of Poisson's equation for the SCM geometry. Task 3 is interpretation of SCM data and technology transfer. Our expertise with interpreting SCM images is being transferred to industry through our software program FASTC2D. The program features an easy to use interface, rapid profile extraction, and operation in a Windows environment.

**DELIVERABLES:** By 2003, demonstrate optimized 3-D calculations of the SCM signal across dopant gradients and junctions.

Currently, the spatial resolution of 2-D dopant profiles measured with the SCM is limited by the tip size and by the data interpretation techniques. One way to overcome the tip size limitation may be to bevel the sample on a cross section, producing magnification both in depth and laterally. We have begun to investigate SCM measurements on beveled samples. While it is straightforward to produce a beveled cross section, carrier redistribution may raise new interpretation issues.

The version of *FASTC2D* currently available utilizes a calibration curve, determined from a database of pre-calculated solutions, which can very rapidly determine a 2-D carrier profile from an SCM image. When used in conjunction with Secondary Ion Mass Spectrometry (SIMS) measurements or a reference sample, relatively accurate profiles can be obtained. We have produced a series of "known good samples," which are intended to be used with *FASTC2D* in a tutorial teaching best measurement and data interpretation procedures. Technical Contact: Joseph J. Kopanski

**Staff-Years (FY 2002):** 3.5 professionals 5 guest researchers

**DELIVERABLES:** By 2004. improve spatial resolution of SCM measured dopant profiles by developing techniques to produce precisely beveled samples and techniques for their interpretation.

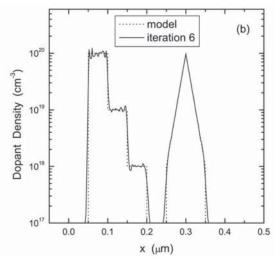

SCM regression solution matched to theoretical dopant profile. Regression solutions provided enhanced spatial resolution and accuracy over calibration curve methods.

A physically accurate 3-D model and determination of the dopant profile by an inverse solution are required to meet industrial needs for 2-D dopant profiling to the end of the ITRS. We have previously developed a quasi-3-D model of the SCM that predicts the essential behavior of the SCM measurement. However, for the required dopant profiling performance goals, a more rigorous approach is necessary. Towards this end, the finite element method has been employed to solve Poisson's Equation for the SCM geometry in three dimensions. Accuracy requirements may also force the consideration of quantum mechanical effects, necessitating the solution of the coupled Poisson and Schrödinger Equations. We are developing improved 3-D Poisson solvers using the LaGriT grid management toolbox in collaboration with Los Alamos National Laboratories.

An inverse solution of the SCM requires repeated solutions of the forward problem; i.e., calculation of the SCM signal from candidate carrier profiles. The candidate carrier profile is adjusted until a carrier profile is found that yields a calculated SCM signal that agrees with the measured SCM signal. Project staff have developed a regression procedure to do this with a 2-D solver. The final level of refinement is to use the full 3-D model as the basis of inverse solutions of the SCM. However, the volume of data to be processed and the time required for calculation make this intractable for routine profile extraction. Practical application requires finding shortcuts that will achieve the 3-D result without having to complete the entire round of 3-D simulations.

**DELIVERABLES:** By 2005, have available for distribution to users a computationally efficient method of determining carrier profiles from inverse solutions of scanning capacitance microscopy based on 3-D models.

The project is also actively investigating other SPM based characterization techniques. We plan to extend the SCM carrier profiling capacity to SiC and III-V semiconductors. Intermittent-contact scanning capacitance microscopy is sensitive to variations in the dielectric constant of thin films and can detect metal layers buried beneath insulating films. Optical pumping of scanning probe microscopes promises to allow determination of carrier recombination and generation lifetimes with unprecedented spatial resolution.

#### ACCOMPLISHMENTS

• Progress in development of SCM 3-D regression solutions. Developed a methodology for calculating the SCM signal by using the oxide-capacitance distribution to specify a natural boundary condition along the probed surface of the semiconductor sample, so that only the semiconductor substrate region needs to be discretized. This approach may lead to a dramatic increase in the speed of which 3-D solutions can be obtained.

• Developed techniques to optically pump scanning probe microscopes. Dr. Gyoung-Ho Buh, guest researcher from the University of Seoul, Korea, has developed techniques to precisely optically pump scanning probe microscopes. The technique encompasses a GUI interface written in Visual C++ to precisely control a laser, lock-in amplifier, and digital oscilloscope to measure optically induced capacitance transients. Publications and a patent application are pending.

■ *Implemented advanced MOS models in FASTC2D*. Implemented new routines to calculate the SCM capacitance-voltage curve database using Fermi-Dirac statistics and either a classical or quantum mechanical model. This is the first implementation of a quantum mechanical correction to the C-V response for SCM data interpretation. Since SCM usually uses a very thin oxide, this is an important extension to previous practice.

• Developed software to simulate the dopant profile exposed on a beveled cross section. The

BASSAR (for Bevel and Section Simulation and Reconstruction) software can (1) simulate 2-D profiles from input model parameters, (2) predict profiles that would be exposed at specified cross sectioning and bevel angles, and (3) recover the normal profile from an input profile measured on a beveled cross section.

SPICE Simulation of SCM Capacitance Sensor. Chi Tran, guest researcher from the University of California, Berkley, and Dr. Buh conducted SPICE simulations of an RCA style capacitance sensor confirming several previously unverified assumptions about the behavior of the SCM. A paper will be submitted to USJ-2003.

Improved optical characterization facility. Dr. Glen Birdwell has extended our photoreflectance capability from a room temperature only measurement, which covered a spectral range of 0.62 eV to 1.8 eV, to a continuously variable temperature system capable of measurements from 15 K to 300 K over a spectral range of 0.5 eV to 3.75 eV. In addition, further upgrades of the optics throughout the system now allow for surface photovoltage measurements from 0.5 eV to 5.6 eV. With these extended capabilities, we are able to investigate a large number of elemental and compound semiconductors. Investigations of antimony-based compounds and devices, transition metal silicides, and IIInitrides are currently in progress.

• Updated resistivity mapping system. The rebuilt and updated system uses a Keithley source/ measure unit (instead of an analog current source and voltmeter) and is controlled by Testpoint (instead of a DOS-based language). A switch matrix to enable simultaneous 2-pt and 4-pt measurements has been procured. A prototype process to produce the contact array and implement resistivity mapping of GaN substrates with 40 micrometer spatial resolution has also been developed.

# FY OUTPUTS

#### COLLABORATIONS

• Agere Systems, Jack Hergenrother, Quantitative SCM of vertical replacement-gate transistors (Joseph J. Kopanski)

• Air Force Research Laboratory, Materials and Manufacturing Directorate, WPAFB, Joe VanNostrand, MBE transferred to WPAFB, DARPA proposal submitted, samples exchanged (Thomas J. Shaffner)  ARL, Paul Amirtharaj, Guest Researcher, Optical characterization metrologies and OA funding strategy (Thomas J. Shaffner)

• ARL, Paul Amirtharaj, optical characterization by surface photovoltage techniques (A. Glen Birdwell)

• ATMI, Danbury, CT, George Brandes and Ed Hutchins, DARPA funded collaboration on IIInitride materials (Thomas J. Shaffner)

• Atolytics Inc., Paul Weiss, State College, PA, Development of ac microwave scanning tunneling microscope, Dept. of Commerce SBIR (Joseph J. Kopanski)

Dynamic Research Corporation, SCM of actively biased SOI MOSFETs (Joseph J. Kopanski)

• Freiberger, M/A-COM, Osemi, AXT, Picogiga, Emcore, Epitronics, IQE, Hall Round-Robin participants (W. Robert Thurber and Thomas J. Shaffner)

Imago Scientific Instruments Corporation, Madison, WI, Tom Kelly, Evaluation of position sensitive atom probe (Thomas J. Shaffner)

Manufacturing Instrumentation Consultant Company, Massood Tabib-Azar, Cleveland, OH, Co-axial AFM probes for near-field microwave and electrical measurements (Joseph J. Kopanski)

• NIST ATP Evaluation Board (Thomas J. Shaffner)

• NIST Division 814, Dick Harris, MBE transferred to Boulder (Thomas J. Shaffner)

• NIST Division 815, Norman Sanford, Wide bandgap nitride materials metrology (A. Glen Birdwell and Thomas J. Shaffner)

• NIST Division 836, Jim Maslar, Raman spectroscopy of wide bandgap nitride materials (Thomas J. Shaffner and A. Glen Birdwell)

• NIST Division 852, Larry Robins, Optical metrology of wide bandgap nitride materials (Thomas J. Shaffner and A. Glen Birdwell)

• NIST Division 855, Albert Davydov, Leo Bendersky, TEM of wide bandgap nitride materials (Thomas J. Shaffner and A. Glen Birdwell)

NIST Division 860, Harold Marshall, Strategy for OA funding (Thomas J. Shaffner)

• NIST Division 841, Dan Pierce, Hall effect and resistivity measurements on GaAs (W. Robert Thurber)

• NIST Division 855, Albert Davydov and Leo Bendersky, Characterization of GaN defects and contacts (Joseph J. Kopanski)

• NIST Division 855, Albert Davydov, Hall effect and resistivity measurements on GaN (W. Robert Thurber)

• North Carolina State University, John Muth, Surface photovoltage analysis of III-nitride materials (A. Glen Birdwell)

• NRL, Brian Bennett, Analysis of InGaSb samples by surface photovoltage and photoreflectance (A. Glen Birdwell)

• Semiconductor Characterization Instruments, Inc., Fred Pollak, PR/SPV characterization and technique development (Thomas J. Shaffner and A. Glen Birdwell)

TriQuint Semiconductor, Dallas, TX, Paul Saunier and Ed Beam, DARPA proposal submitted in joint collaboration and exchange of III-V and GaN samples (Thomas J. Shaffner and A. Glen Birdwell)

• University of Missouri-Rolla, Matt O'Keefe, and Wright State University, David Look, DARPA proposal submitted to in joint collaboration with NIST and WPAFB. Proposed work covered electron microscopy and electrical characterization of III-nitride and novel chalcopyrite materials (Thomas J. Shaffner)

• University of North Texas, Chris Littler/Terry Golden, Collaboration of GaAsSb by modulation spectroscopy metrology (A. Glen Birdwell)

University of North Texas, Denton, TX, Chris Littler, Collaboration on III-V modulation spectroscopy metrology (Thomas J. Shaffner)

# **RECENT PUBLICATIONS**

J.J. Kopanski, "Capacitive Probe Microscopy," Encyclopedia of Imaging Science and Technology, pp. 16-31 (15-JAN-2002).

# Advanced MOS Device Reliability and Characterization

## GOALS

To provide electrical and reliability measurement techniques, data, physical models, and fundamental understanding for ultra-thin silicon dioxide and alternate gate dielectrics in future Metal Oxide Semiconductor (MOS) devices. To increase the understanding of the relationship between the gate dielectric material/interface properties and device electrical and reliability measurements.

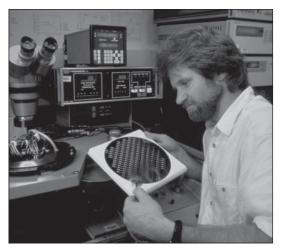

John Suehle loading a test wafer on a wafer prober for long-term dielectric testing.

# **CUSTOMER NEEDS**

The Semiconductor Industry Association's (SIA's) International Technology Roadmap for Semiconductors indicates that the equivalent thickness of the gate dielectric will need to be 1.0 nm to 1.5 nm by 2004. Due to increased power consumption, intrinsic device reliability, and circuit instabilities associated with SiO<sub>2</sub> of this thickness, a high-permittivity gate dielectric (e.g., Si<sub>3</sub>N<sub>4</sub>, HfSixOy, ZrO<sub>2</sub>) with low leakage current and at least equivalent capacitance, performance, and reliability will be required. The physics of failure and traditional reliability testing techniques must be re-examined for ultra-thin gate oxides that exhibit excessive tunneling currents and soft breakdown. Electrical characterization of MOS capacitors and Field Effect Transistors (FETs) have historically been used to determine device and gate dielectric properties such as insulator thickness, defect densities, mobility, substrate doping, bandgap, and reliability. Electrical and reliability characterization methodologies need to be developed and enhanced to address issues associated with both ultra-thin SiO<sub>2</sub> and alternate dielectrics including large leakage currents, quantum effects, and thickness dependent properties. As compared to SiO<sub>2</sub>, very little is known about the physical or electrical properties of high dielectric constant gate dielectrics in MOS devices. The use of these films in Complementary Metal Oxide Semiconductor (CMOS) technology requires a fundamental understanding of the relationship between the gate dielectric material/interface and device electrical and reliability measurements.

# **TECHNICAL STRATEGY**

The strategy of this effort will be to obtain or fabricate both device samples and blanket films, to perform reliability and electrical characterization of the devices, and to collaborate with other researchers to perform analytical characterization. Many issues such as tunnel/leakage current and spatially dependent properties associated with metal oxide and silicate dielectrics are also present in ultra-thin oxide and oxide-nitride stacked dielectrics. Therefore, many of the characterization schemes will first be developed on the simpler ultra-thin oxide and oxide-nitride dielectrics and then applied to the metal oxide and silicate dielectrics.

There are two main focus areas for this project. The first focus area investigates the physics of failure and the reliability testing techniques for ultrathin SiO<sub>2</sub> and high dielectric constant gate dielectrics. The physical mechanism responsible for "soft" or "quasi" breakdown modes in ultra-thin SiO<sub>2</sub> and high- $\kappa$  films and its implications for device reliability will be investigated as a function of test conditions and temperature. Long-term timedependent-dielectric breakdown (TDDB) tests will be conducted on SiO<sub>2</sub> films and high- $\kappa$  dielectrics with equivalent oxide thickness (EOT) as thin as 1.5 nm at electric fields close to operating conditions. These tests will be used to determine the thermal and electrical acceleration parameters of device breakdown.

**DELIVERABLES:** By 2003, studies of the long-term wear-out and breakdown of advanced high- $\kappa$  dielectrics.

Experiments will be conducted to investigate the differences of gate oxide breakdown and wear-out due to high oxide field and hot-carrier injection. This study will provide insight into the physical

Technical Contact: John S. Suehle

Staff-Years (FY 2002):

- 2 professionals

- 1 technician 3 guest researchers

mechanism of ultra-thin and high- $\kappa$  gate oxide wearout and breakdown.

**DELIVERABLES:** By 2003, experimental results of charge stability and trapping in  $HfO_2$  films including defect generation rates due to constant voltage stress.

The understanding generated in this research will be used to continue generating standard measurements through a NIST-coordinated collaboration between EIA-JEDEC (Electronic Industries Association Joint Electron Device Engineering Council) and the ASTM (American Society for Testing and Materials). Studies on the reliability of high dielectric constant dielectrics also will be performed.

**DELIVERABLES:** By 2004, a new JEDEC standard, including guidelines for performing capacitance-voltage (CV), conductance-voltage (GV), and charge pumping measurements on ultra-thin SiO<sub>2</sub> and high- $\kappa$  films for extracting parameters such as EOT, Interface State Density (D<sub>u</sub>), V<sub>ED</sub>, etc.

A low-noise (fA), high-temperature (300 °C) probe station is used to electrically characterize devices.

The second focus area investigates electrical measurement techniques, procedures, and analysis associated with devices having thin oxide and alternate gate dielectrics. The electrical measurement techniques that we are investigating include capacitance-conductance characterization, dielectric tunnel and leakage current characterization, and defect density measurements such as charge pumping and conductance. Furthermore, standard properties and mechanisms/correlations for these dielectrics, including defect centers, dielectric constant, defect generation rates, and leakage/tunnel current, will be characterized. **DELIVERABLES:** By 2003, experimental studies on the effect of annealing and aluminum concentration on the charge trapping characteristics of  $HfO_2$  gate dielectrics.

High-K gate dielectric films will be obtained from key industrial and university groups. Electrical characterization methodologies will be developed to address various issues associated with these films, including large leakage currents, quantum effects, thickness dependent properties, large trap densities, transient (non-steady state) behavior, unknown physical properties, and the lack of physical models.

Examples of measurement problems that are being addressed include modifying and verifying electrical defect density measurement techniques, including conductance-frequency, capacitance-voltage, and charge-pumping.

#### Accomplishments

• New JEDEC document including noise-based test procedures for TDDB standard of sub-2 nm films. The document includes new test methodologies for detecting soft or noisy breakdown events in ultra-thin gate dielectrics and is expected to be effective in detecting breakdown in films as thin as 1.5 nm. It has been approved by the JEDEC JC-14.2 Committee and is undergoing final ballot by the JEDEC Council. A round-robin experiment is currently being planned to investigate the effectiveness of the test procedure.

Negative bias temperature instability studied for deep sub-micro p-MOS devices under pulsed bias stress. Bias Temperature Instability (BTI) has become a serious reliability problem in deep sub-micron p-MOSFETs as device dimensions are continually scaled down. The  $\Delta V$ th of negative bias temperature instability (NBTI) was observed to be significantly reduced for pulsed bias repetition frequencies greater than 10 kHz, implying an important role of hole trapping and detrapping. However,  $\Delta V$ th of positive bias temperature instability (PBTI) was almost independent of frequency. The  $\Delta V$ th did not show significant channel length dependency. These results suggested that there are different mechanisms for  $\Delta V$ th of NBTI and NBTI, and the reliability specifications of NBTI could possibly be relaxed under certain pulsed operation conditions.

• A study was performed to investigate defect generation in ultra-thin silicon dioxide films over large fluence ranges. The defect generation rate (P<sub>v</sub>) during constant voltage stress was investigated by using short-time voltage pulses over a large fluence range. It was found that  $P_g$  is not constant as a function of injected charge, and the voltage acceleration of  $P_g$  in the linear defect generation regime is similar to that of the reciprocal of  $Q_{BD}$ . The change of carrier capture cross ( $\sigma$ ) during defect generation was speculated as one of the reasons responsible for the change of  $P_g$  value. However, from this preliminary report, we have determined that the change of  $P_g$  cannot be explained by the change of  $\sigma$ .

• A Visual Basic MOS simulation code was developed based on first-order approximations for the quantum mechanical (QM) effects. The code, which permits us to evaluate experimental and simulation parameters on CV characteristics quickly, was developed. Comparisons with full Schroedinger-Poisson solvers (UTQuant) showed good agreement over a large range of experimental conditions ( $t_{ox} = 1.0$  nm to 2.0 nm, Nsub =  $10^{15}$  cm<sup>-3</sup> to  $10^{18}$  cm<sup>-3</sup>). The results show that a model based on the modification of the total semiconductor charge can be used to simulate QM CV characteristics of polysilicon-gated MOS devices.

The effects of a distribution of interface states with energy on the CV characteristics can be simulated. Further work on the impact of bulk insulator defects (slow states), EOT extraction, etc. can now begin. The code is currently being used in collaboration with J. Kopanski in *FASTC2D* applications.

CV-software was completed which permits simulation of the frequency dependent interface state capacitance. The software was transferred to, and is being used by, International SEMATECH.

A joint collaboration between NIST and the Jet Propulsion Laboratory (JPL) investigated what effect ionizing radiation experienced in deep space missions will have on the reliability of ultra-thin gate dielectrics. It has been previously reported that heavy ion bombardment can cause radiation-induced soft breakdown (RSB) in ultrathin gate dielectrics. Constant voltage TDDB distributions were obtained for both un-irradiated and irradiated 3.0 nm and 3.2 nm thick SiO<sub>2</sub> films subjected to 60Co gamma irradiation and heavy ions of 823 MeV<sup>129</sup>Xe (Linear Energy Transfer, LET = 59 MeV cm<sup>2</sup>/mg). The gamma irradiation had no effect on oxide lifetime. Under heavy ion irradiation, lifetime degradation was observed for devices with zero gate voltage applied, suggesting that even powered down circuits may be at risk for long-term missions in ionizing radiation environments. The reduction of oxide lifetime under constant-voltage

stress conditions was a strong function of the heavy ion fluence.

### FY OUTPUTS

#### Collaborations

• Advanced Micro Devices, Ultra thin oxide reliability (John S. Suehle)

- Agere Technologies, Ultra-thin gate oxide reliability (John S. Suehle)

- Analog Devices, Limerick, Ireland, Ultra-thin gate oxide reliability (John S. Suehle)

- The George Washington University, Microhotplate-based chemical sensors (John S. Suehle)

- Motorola, Ultra-thin gate oxide reliability (John S. Suehle)

- N.C. State University (oxynitrides, nitrides, ultra-thin SiO<sub>2</sub>), Alternative gate dielectrics (Eric M. Vogel)

National Semiconductor, Ultra-thin gate oxide reliability (John S. Suehle)

- NIST Division 836, Microhotplate-based sensor arrays (John S. Suehle and Michael Gaitan)

- NIST Divisions 836, 837, 838, Dr. Roger van Zee et al., Molecular Electronics Competence Project (Curt A. Richter and John S. Suehle)

- NIST Divisions 836, 837, 838, Roger Van Zee, et al., Spectroscopic ellipsometry of molecular electronics (Nhan V. Nguyen, Curt A. Richter, and John S. Suehle)

- Penn State University, Ultra-thin gate oxide reliability (John S. Suehle)

- Sharp Microelectronics, Dr. John Conley, Characterization of Hafnium-oxide dielectric films (James R. Ehrstein and John S. Suehle)

- Texas Instruments, Electrical and reliability characterization of ultra thin gate oxides (John S. Suehle and Curt A. Richter)

- Texas Instruments, Ultra-thin gate oxide reliability (John S. Suehle)

- The Pennsylvania State University, Molecular electronics (Curt A. Richter and John S. Suehle)

- University of Delaware, Alternative dielectrics (John S. Suehle)

• University of Maryland, College Park, Microhotplate-based chemical sensors (John S. Suehle)

• University of Maryland, College Park, Ultrathin gate oxide reliability (John S. Suehle)

University of Maryland, Gate dielectric reliability (Eric M. Vogel)

University of Minnesota, Alternate Gate Dielectrics (Eric M. Vogel)

#### **STANDARDS COMMITTEE PARTICIPATION**

JEDEC JC14.2 Committee on Wafer-Level Reliability, Dielectric Working Group, Chairman (John S. Suehle)

#### **RECENT PUBLICATIONS**

J.F. Conley, J.S. Suehle, A.H. Johnston, B. Wang, T. Miyahara, E.M. Vogel, J.B. Bernstein, "Heavy Ion Induced Soft Breakdown of Thin Gate Oxides," IEEE Trans. on Nuclear Science, Vol. 48, No. 6, pp. 1913-1916, (01-DEC-2001).

C.A. Richter, J.S. Suehle, M.D. Edelstein, O. Kirillov, R.D. van Zee, "Molecular Electronic Test Structures," Bulletin of the American Physical Society, Vol. 47, No. 1, pp. 285-285, (01-MAR-2002).

J.S. Suehle, "Ultra-Thin Gate Oxide Reliability: Physical Models, Statistics, and Characterization," IEEE Trans. on Electron Dev., Vol. 49, No. 6, pp. 958-971, (01-JUN-2002).

J.S. Suehle, B. Wang, J.F. Conley, E.M. Vogel, P. Roitman, C.E. Weintraub, A.H. Johnston, J.B. Bernstein, "Observation of Latent Reliability Degradation in Ultra-Thin Oxides after Heavy-Ion Irradiation," Applied Physics Letters, Vol. 80, No. 7, pp. 1282-1284, (18-FEB-2002).

E.M. Vogel, D. Heh, J.B. Bernstein, "Interaction Between Low-energy Electrons and Defects Created By Hot Holes in Ultra-Thin Silicon Dioxide," Applied Physics Letters, Vol. 80, No. 18, pp. 3343-3345, (06-MAY-2002).

E.M. Vogel, M.D. Edelstein, J.S. Suehle, "Reliability of Ultra-Thin Silicon Dioxide Under Substrate Hot-Electronic, Substrate Hot-Hole, and Tunneling Stress," Microelectronics Engineering, pp. 1-11, (01-NOV-2001).

C.E. Weintraub, E.M. Vogel, J.R. Hauser, N. Yang, V. Misra, J.J. Wortman, J.J. Ganem, P. Masson, "Study of Low-Frequency Charge Pumping on Thin Stacked Dielectrics," IEEE Transactions on Electron Devices, Vol. 48, No. 12, pp. 2754-2762, (01-DEC-2001).

# NANOELECTRONIC DEVICE METROLOGY

#### GOALS

The overall goal of the Nanoelectronic Device Metrology (NEDM) Project is to develop the metrology that will help enable new nanotechnologies (such as molecular electronics and Si-based quantum devices) to supplement and/or supplant conventional Complementary Metal Oxide Semiconductor (CMOS) devices. This involves determining the critical metrology needs for these exploratory technologies. One specific goal is to develop test structures and methods to measure reliably the electrical properties of small ensembles of molecules. A second targeted goal is to develop the precise metrology and characterization methods required for the systematic characterization of Si-based nanoelectronic devices.

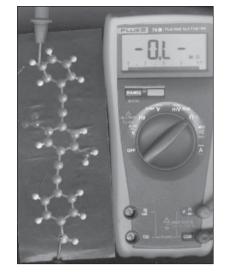

*Curt Richter loads a molecular electronic sample for electrical characterization. Copyright Robert Rathe*

## **CUSTOMER NEEDS**

The CMOS FET (Field Effect Transistor), which is the current basis of ULSI (Ultra-Large-Scale Integration) circuits, is beginning to show fundamental limits associated with the laws of quantum mechanics and the limitations of fabrication techniques. The Semiconductor Industry Association's (SIA's) International Technology Roadmap for Semiconductors (ITRS) shows no known solutions by 2005 for a variety of technological requirements including gate dielectric, gate leakage, and junction depth. Therefore, it is expected that entirely new device structures and computational paradigms will be required to augment and/or replace standard planar CMOS devices. Two post-CMOS technologies that show promise to extend traditional scaling laws for increased computational performance beyond the limits of conventional CMOS are molecular electronics and Sibased quantum electronic devices.

Molecular electronics (ME) is a field that many predict will have important technological impacts on the computational and communication systems of the future. In ME systems, molecules perform the functions of electronic components. Research and development for silicon-based nanoelectronics (e.g., wrap-around FETs, Si-based RTDs [resonant tunneling diodes], silicon quantum dots) for the post-CMOS era are currently of interest due to their inherent compatibility with CMOS technology.

The NEDM Project is concerned with fundamental research related to possible future devices that will replace or augment standard CMOS technology. In order to ensure that our research is technically relevant, we plan to align ourselves with research described by the Microelectronics Advanced Research Corporation (MARCO), alluded to in the SIA's Roadmap and other similar semiconductor industry organizations and documents.

The industry for these emerging nanoelectronic devices will require reference data, standards, precision measurement protocols, and standardized test structures and associated measurement protocols to develop into a viable commercial technology. The ultimate objective of this project is to provide the measurement infrastructure to aid this development. Through strong ties with industry leaders and cutting-edge researchers, we are accelerating the pace of our program and focusing our research on the most relevant technologies.

## **TECHNICAL STRATEGY**

The NEDM Project investigates and is developing metrology for two specific areas of nanotechnology: molecular electronics and Si-based quantum electronics.

In ME, our major objectives are:

- A NIST standard suite of molecular test structures.

- Fundamental understanding of charge transport through molecules and molecular ensembles.

We plan to develop robust molecular test structures and use them to measure the electrical properties of molecules. Specifically, we are developing test-structures based upon nanofabrication and NEMS (Nano-Electro-Mechanical Systems) Technical Contact: Curt A. Richter

Staff-Years (FY 2002): 3.5 professionals 0.5 technician 2 guest researchers

"...there is no particular reason why Moore's law should continue to hold: it is a law of human ingenuity, not of nature. At some point, Moore's law will break down. The question is when?"

> Seth Lloyd, d'Arbeloff Laboratory for Information Systems and Technology, Massachusetts Institute of Technology

"If individual molecules can be made to process information, they could be the answer to the computer industry's prayers."

> P. Ball, Consultant Editor, Nature, vol. 406, 13 July, 2000, pp. 118-120

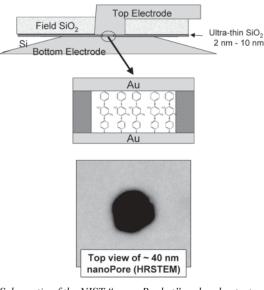

processing techniques for assessing the electrical properties and reliability of moletronic molecules. (One example, the "nano-Bucket," is illustrated on page 12.) Molecules will be incorporated into the test structures via self-assembly to form high-quality SAMs (self-assembled monolayers). In addition to the complexity of the nanofabrication of test structures, the challenges associated with measuring the electrical properties (such as current-voltage and capacitance-voltage as functions of temperature and applied fields) of these small molecular ensembles are daunting. The measured electrical properties will be correlated with systematic characterization studies by a variety of advanced analytical probes and the results used in the validation of predictive theoretical models.

Electrically measuring molecules: the concept.

The new Si-nanotechnology effort will focus on physical and electrical metrology of the basic building blocks of silicon quantum electronic devices (e.g., quantum layers, wires, and dots of silicon surrounded by silicon dioxide). By identifying and addressing the critical metrology issues associated with these basic building blocks, the basis of metrology for future Si-based ULSI nanotechnology will be defined.

A major goal is to fabricate single quantum dots and wires with controllable size. These will be used to establish the relationship between the key fabrication conditions, physical properties (such as the geometry of the quantum-dot and the tunneling barrier), and final electrical properties of these floating silicon devices (i.e., metal-oxide-silicon-oxidesilicon [MOSOS] devices). Production of MOSOS capacitor structures is an intermediate step en route to this end goal. This research will provide the information necessary to help identify and address the necessary electrical and physical characterization methodologies.

Developing the metrology for "beyond-CMOS" nanoelectronic devices is a challenging and multidisciplinary task; therefore, it is important to be teamed with strong collaborators. The ME staff is part of a NIST Competence Project with the Chemical Science and Technology Laboratory (CSTL). CSTL provides the bulk of the molecules we will use, provides insights into SAM formation, performs precise structural characterization, and performs advanced quantum chemistry theoretical analysis. In addition, the ME team is working with various companies, universities, and government laboratories (e.g., Hewlett-Packard (HP), Yale University, University of North Texas, Naval Research Labs). The quantum Si device team is working closely with NIST's Electricity Division to study Si-based single-electron tunneling devices.

**DELIVERABLES:** By 2003, characterize and optimize preferred molecular electronic test structure (METS). NIST Special Publication and/or manuscript prepared and submitted.

**DELIVERABLES:** By 2003, correlation of the physical properties of self-assembled quantum dots with the processing parameters used to form them. Manuscript prepared and submitted.

**DELIVERABLES:** By 2005, complete a documented NIST standard suite of molecular electronic test structures.

**DELIVERABLES:** By 2005, quantum-dot memory field effect transistors (QD FETs): Experimental correlation of the final performance and electrical properties of QD FETs with the physical properties obtained from precise physical characterization. Manuscript prepared and submitted.

#### ACCOMPLISHMENTS

Establishing Infrastructure for the Nanoelectronic Device Metrology Project. In FY 2002, the Nanoelectronic Device Metrology Project was established. Extensive plans were developed and funding was acquired for this project. There are three areas of infrastructure that have been improved: personnel, equipment, and funding. In addition to the joint CSTL/EEEL Molecular Electronics Competence (started FY01) and funding from the National Nanotechnology Initiative (started mid-year FY01), the NEDM Project is part of two recently funded ATP Intramural Awards (for 2002), "The Missing Plateau: Confined Silicon Devices for ULSI Nanotechnology," (EEEL/MSEL) and "Model-Guided Screening of Electrically-Active Molecules for Nanoelectronics" (CSTL/EEEL).

Personnel. Since Sep. 2001, four full-time researchers have joined the NEDM Project. Oleg A. Kirillov (a recent graduate of Rochester Institute of Technology's [RIT's] process engineering program) was hired as a processing engineer. Dr. Jin-Wan Park (Seoul National University) and Dr. Jin-Ping Han (Yale University) joined the NEDM Project as guest researchers and are concentrating their efforts on the Si-Based Quantum Devices Task. Dr. Christina Hacker (U. Wisconsin at Madison) most recently joined the NEDM Project as a postdoctoral candidate through the NRC Research Associate Program. Dr. Hacker is investigating hybrid Si/molecular technologies.

• Nanoelectronic Equipment Infrastructure. A substantial portion of the first year was spent in vastly improving our nanoelectronic equipment infrastructure. A new backside mask aligner and an oil-free metal deposition system have been installed. The installation process is underway for a plasma deposition and etching system. This new equipment combined with our growing expertise and the existing capabilities (including electron-beam lithography) in the Microfabrication Process Facility, give us fabrication capabilities near the forefront of nanoelectronic research.

• Development of nano-Bucket Fabrication Processes. Individual nano-Bucket devices have been fabricated. Key processing steps (that combine NEMS techniques with planar integrated circuit processing methods) have been developed for the nano-Bucket. The critical steps are suspension of thin Si membranes, electron-beam lithography to define the nanopore, base metal deposition, self assembly of a molecular monolayer, and deposition of metal on top of the molecules without destroying or electrically shorting through them.

Prototypical Multiple-Quantum-Dot-Island Floating Body Devices. Processing parameters have been established to reproducibly control the size distribution, concentration, and shape of silicon quantum dots formed using LPCVD (Low Pressure Chemical Vapor Deposition). Two methodologies for forming silicon quantum dots have been explored. The first is by direct deposition of polycrystalline quantum dots using LPCVD at short deposition times. The second is by deposition of thin amorphous silicon layers using LPCVD followed by annealing. Quantum-dot island floating body capacitors and transistors will be made by using these quantum dot formation techniques. A simple two-level capacitor mask set and a four-level

mask set to fabricate field-oxide isolated, polysilicon gated, field effect transistors (FETs) have been designed and purchased. Working polysilicon gated capacitors (without the floating quantum dots) have been fabricated with gate oxide thicknesses of approximately 5 nm, and processes have been developed to form gate oxides with thicknesses of approximately 2 nm.

Alternate Molecular Electronic Test Structures. Initial assessment of the capabilities of alternate molecular electronic test structures (based upon cross bars) have been made. Cross-bar structures based upon shadow masks have been fabricated from a variety of metal systems (Au-Au, Al/ AlOx-Al, Al-Pt) and electrically characterized by current-voltage and capacitance-voltage measurements. A working demonstration of "molecular doorbells," a prototype flip-chip test structure, has also been implemented. Fabrication processes were developed for these flip-chip structures and an apparatus was set up to apply a controllable, constant force to the flexible top layer to bring the top metal down to contact the base. Experimentally, the system was characterized without molecules (when the metals short). A monolayer of octadecanethiol was self assembled onto Au lines on a mica top electrode and electrically measured. The initial results — that the Au lines do not short - are promising.

Quantum dot floating island capacitor.

Molecular Electronic Test Structure (METS) Assessment Methodology. An effective test protocol was developed for METS to ensure that electrical results can be attributed to the molecules and are not an artifact of the test structure itself. Current-voltage curves were obtained for devices with no molecules and for devices containing long-chain alkane-thiols (such as octadecanethiol). These two limits, a conducting short and an insulating film in the nanopore, respectively, characterize the METSs and allow the properties of conducting molecules of interest to be measured reliably. In addition to applying this methodology to the METSs being fabricated in the NEDM Project, we apply these techniques to investigate METSs of other researchers. For example, we have characterized Si<sub>3</sub>N<sub>4</sub>-based nanopore devices in a collaboration with Yale University (M. A. Reed).

• *Electrical Characterization of Molecules.* We developed an initial suite of electrical test procedures for molecular devices. In collaboration with HP Laboratories, we were the first researchers to independently confirm electrical current-voltage characteristics of moletronic devices supplied by HP. Also, we made the world's first ever capacitance-voltage characterizations of self-assembled molecules by using these structures from HP.

*Schematic of the NIST "nano-Bucket" molecular test structure.*

# FY OUTPUTS

#### Collaborations

Hewlett-Packard, R. Stanley Williams, Interface properties of molecular electronic test structures (Curt A. Richter)  Naval Research Laboratories, Ranganathan N.

Shashidhar, Molecular test structure assessment (Curt A. Richter)

NIST Division 837, Dr. L. Richter, Optical characterization of semiconductor interfaces (Curt A. Richter)

• NIST Division 837, John Henry Scott, highresolution TEM studies of molecular test structures (Curt A. Richter)

• NIST Divisions 836, 837, 838, Dr. Roger van Zee et al., Molecular Electronics Competence Project (Curt A. Richter and John S. Suehle)

NIST Divisions 836, 837, 838, Roger Van Zee, et al., Spectroscopic ellipsometry of molecular electronics (Nhan V. Nguyen, Curt A. Richter, and John S. Suehle)

• The Pennsylvania State University, Molecular electronics (Curt A. Richter and John S. Suehle)

• U. Texas at Austin, Prof. Jack Lee, Optical properties of  $ZrO_2$  and  $HfO_2$  for use as high- $\kappa$  gate dielectrics (Curt A. Richter and Nhan V. Nguyen)

• University of Maryland, L. Sita (Chemistry) and M. Faker (Physics), Single molecule test structure via electromigration (Curt A. Richter)

• University of North Texas, Fast molecular electronic test structures (Curt A. Richter)

University of Wisconsin, Madison, Molecular monolayers on Si (Curt A. Richter)

■ Yale University, Prof. M. A. Reed, Robust molecular electronic test structures (Curt A. Richter)

#### **EXTERNAL RECOGNITION**

Elevated to IEEE Senior Member status (Curt A. Richter)

# **RECENT PUBLICATIONS**

Y.J. Cho, N.V. Nguyen, C.A. Richter, J.R. Ehrstein, B.H. Lee, J.C. Lee, "Spectroscopic Ellipsometry Characterization of High- $\kappa$  Dielectric HfO<sub>2</sub> Thin Films and the High-Temperature Annealing on Their Optical Properties," Applied Physics Letters, Vol. 80, No. 7, pp. 1249-1251, (18-FEB-2002).

C.A. Richter, J.S. Suehle, M.D. Edelstein, O. Kirillov, R.D. van Zee, "Molecular Electronic Test Structures," Bulletin of the American Physical Society, Vol. 47, No. 1, pp. 285-285, (01-MAR-2002).

# THIN-FILM PROCESS METROLOGY

## GOALS

Develop new and improved electrical and optical measurements, models, data, and reference materials to enable better and more accurate measurements of select, critical, thin-film parameters for silicon Complementary Metal Oxide Semiconductor (CMOS) technology. Major focus is placed on requirements for oxynitrides, and metal-oxide and metal-silicate films and stacks for advanced gate dielectrics detailed in the International Technology Roadmap for Semiconductors (ITRS).

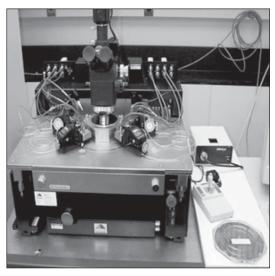

Nhan Van Nguyen (left) and Yong Cho (right) aligning a sample on a custom-built high-accuracy spectroscopic ellipsometer.

## **CUSTOMER NEEDS**

The evolving decrease of the gate dielectric film thickness to an oxide-equivalent value of 1 nm is identified as a critical front-end technology issue in the Semiconductor Industry Association's (SIA's) ITRS. For effective gate dielectric thicknesses below ~2.0 nm, SiO<sub>2</sub> is being replaced, initially by oxynitrides or oxide/nitride stacks, and then by either metal-oxides or metal-silicates. Process control tolerance needs for dielectric thickness are projected to be  $\pm 4 \%$  (3  $\sigma$ ), which translates to less than 0.1 nm for 2 nm films. Requirements for process control measurements are a factor of ten smaller.

Spectroscopic ellipsometry (SE) is expected to continue as the preferred measurement for process monitoring of future gate dielectric films. Industry metrology needs not only improved methods to determine film thickness accurately, but also (1) techniques to determine the structure of the individual films and the interfaces between them; (2) understanding of the relationship between physical, electrical, and optical determinations of film properties; and (3) mechanisms, such as reference materials, for traceability of measurements to NIST to support film metrology.

In order for SE to meet process control requirements of film thickness and unambiguously determine film composition and morphology, the optical properties of these advanced dielectric film systems must be characterized and understood.

# **TECHNICAL STRATEGY**

This project focuses on the issues of (1) developing and providing the basis for traceability to NIST for film thickness measurements; (2) identifying structural models and developing preferred optical index dispersion functions or data for improved ellipsometric analysis of future-generation gate dielectric film systems; and (3) correlating optical, electrical, and physical measurements of thickness, composition, and interface structure.

#### Establish and Transfer Basis of Accuracy for Thin Dielectric Films

Industry requirements for future thin dielectric film optical measurements and calibration standards were identified at a recent NIST-sponsored workshop. Core ellipsometry measurement capability is being expanded and strengthened to meet these requirements. An investigation has been started into cleaning and recontamination issues for film calibration standards to determine whether a workshop-expressed goal of 0.015 nm long-term reproducibility of reference artifact values is obtainable. Procedures are being developed to enable traceability of instrument accuracy to NIST for suppliers of secondary thin-film reference materials without requiring volume production of NIST Standard Reference Materials (SRMs).

**DELIVERABLES:** By 2003, develop and evaluate prototype procedures that will enable traceability to NIST for 1<sup>st</sup> level commercial suppliers of reference materials for oxide films down to 2 nm.

#### Structural and Optical Models for Ellipsometry

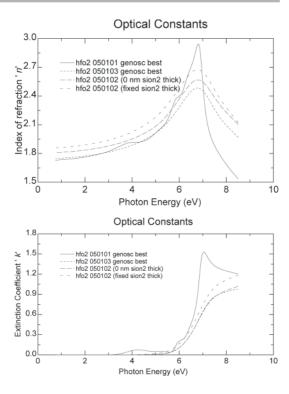

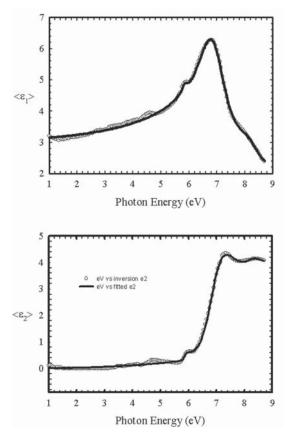

A custom-built, high-accuracy spectroscopic ellipsometer with a spectral range of 1.5 eV to 6 eV is being used for this task, and project staff are working with International SEMATECH, integrated circuit (IC) industry companies, and SRC university staff to obtain and optically characterize advanced oxynitrides, oxide/nitride stacks, and metal oxide and silicate films such as zirconium oxide and hafnium silicate. Characterization will be extended to 8.5 eV to include important optical Technical Contact: James R. Ehrstein

#### Staff-Years (FY 2002):

3.1 professionals

0.5 technician

1.2 guest researchers

index structure of these films beyond their bandgaps. This work is directed at determining preferred structural models, spectroscopic index of refraction values, or preferred optical dispersion functions for each of these film systems, and, where possible, the variability of these parameters due to differences in film fabrication processes. Analysis is done with software developed by NIST for spectroscopic ellipsometry; this software allows maximum flexibility for the addition of the latest published or custom-developed optical response models as appropriate for each material system investigated.